US 20070001945A1

(19) United States

(12) Patent Application Publication

YOSHIDA et al.

(10) Pub. No.: US 2007/0001945 A1

(43) Pub. Date: Jan. 4, 2007

(54) DISPLAY DEVICE AND DRIVING METHOD THEREOF

(75) Inventors: Yasunori YOSHIDA, Atsugi (JP); Hajime KIMURA, Atsugi-shi (JP); Shunpei YAMAZAKI, Tokyo (JP)

Correspondence Address:

FISH & RICHARDSON P.C.

P.O. BOX 1022

MINNEAPOLIS, MN 55440-1022 (US)

(73) Assignee: SEMICONDUCTOR ENERGY LABORATORY CO., LTD., Atsugi-shi (JP)

(21) Appl. No.: 11/427,242

(22) Filed: Jun. 28, 2006

(30) Foreign Application Priority Data

Jul. 4, 2005 (JP) ..... 2005-194600

Publication Classification

(51) Int. Cl.

G09G 3/36 (2006.01)

(52) U.S. Cl. ..... 345/87

(57) ABSTRACT

In an EL display device which performs area grayscale display, image quality is improved and stabilized. A plurality of subpixels each having light emitting elements which emit light of approximately the same color and a plurality of monitor pixels each having the same number of subpixels as the pixel are provided. The light emitting element in the monitor pixel is manufactured at the same time as the light emitting element in the pixel, and the electrode of the light emitting element in the monitor pixel is connected to a different constant current source in each subpixel. A circuit for changing a potential of the electrode of the light emitting element in the pixel for each subpixel in accordance with a potential change of the electrode of the light emitting element of the monitor pixel, thereby the aforementioned purposes are achieved.

FIG.1

FIG.2

FIG.3

FIG.4

FIG.5

FIG.6A

FIG.6B

FIG.7A

FIG.7B

FIG.8A

**FIG.8B**

FIG.9A

FIG.9B

FIG.10

FIG.11A

FIG.11B

FIG.11C

FIG.12

FIG.14

**FIG.15B**

FIG.16A

FIG.16B

FIG.16C

FIG.16D

FIG.16F

FIG.16E

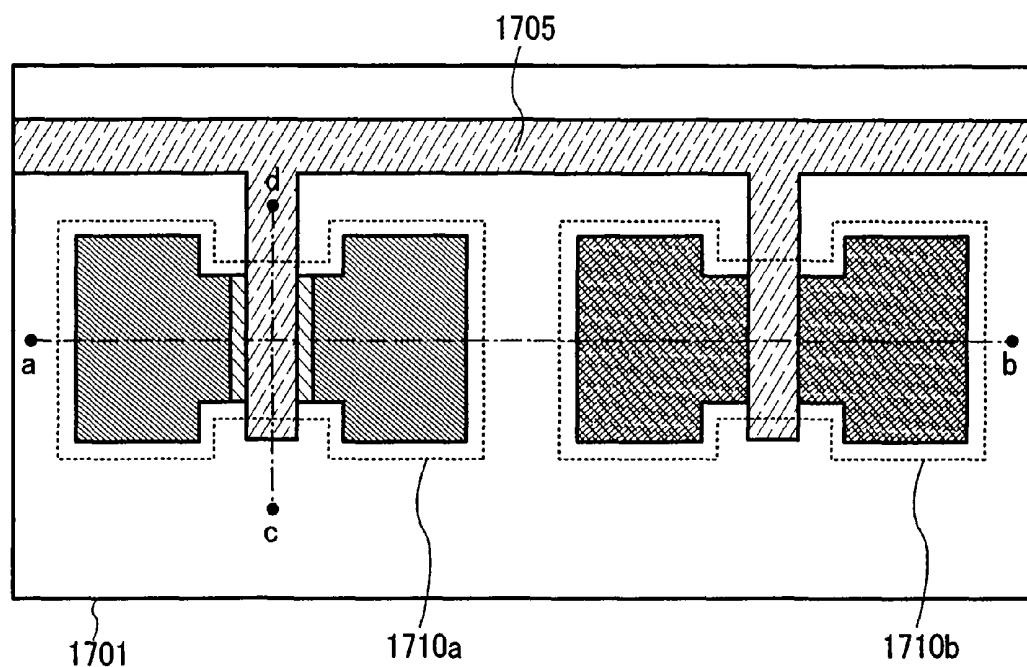

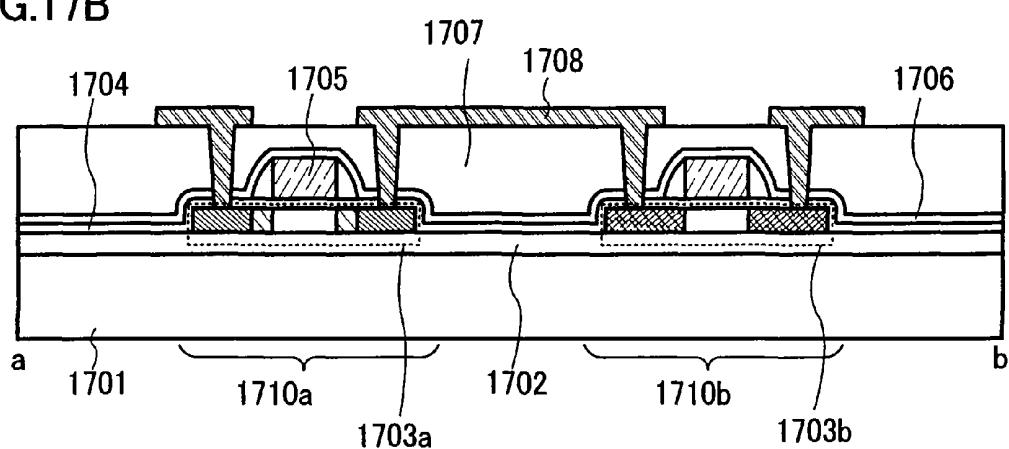

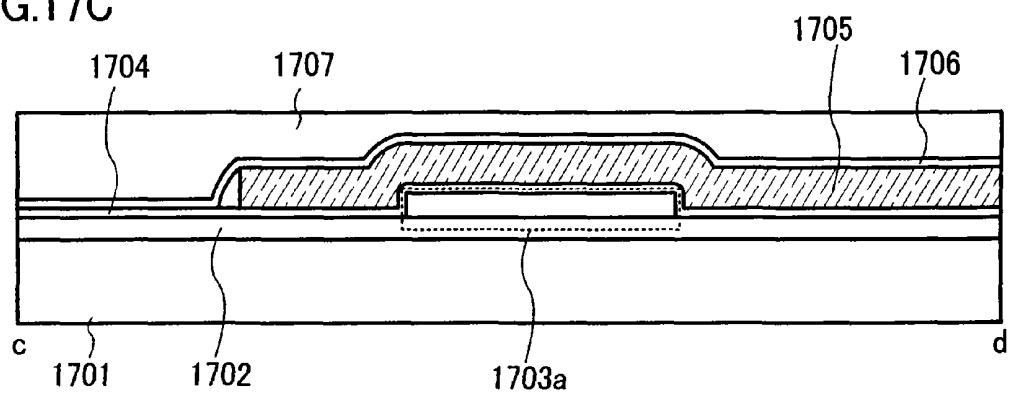

FIG.17A

FIG.17B

FIG.17C

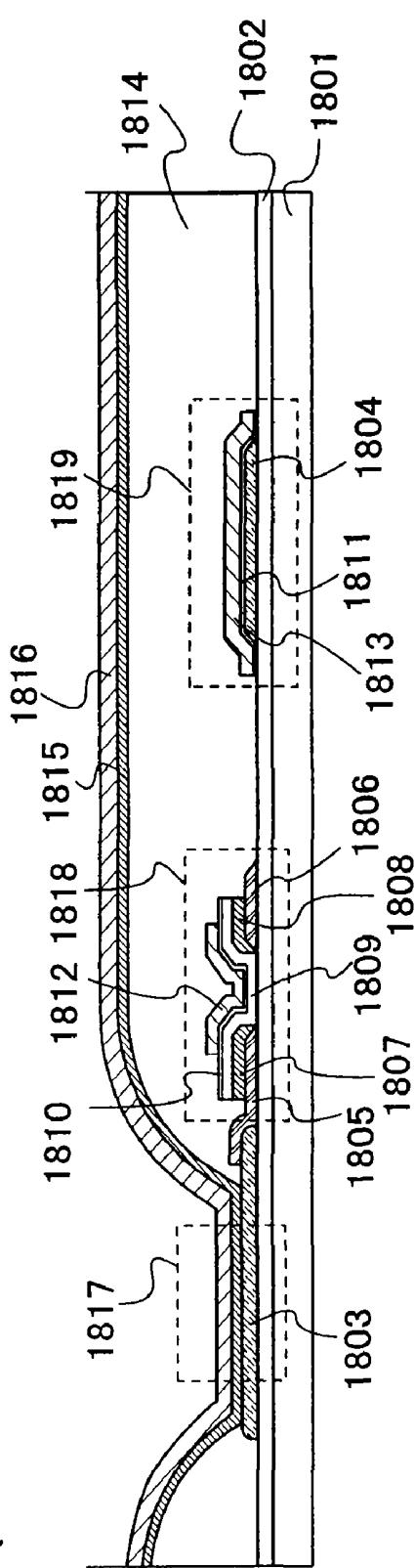

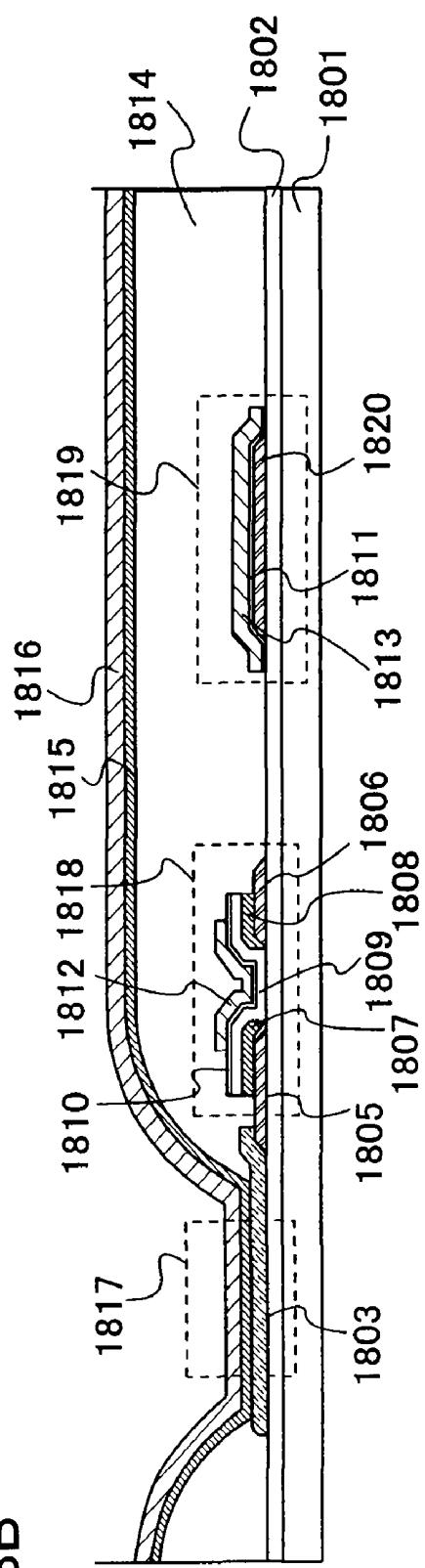

FIG. 18A

FIG. 18B

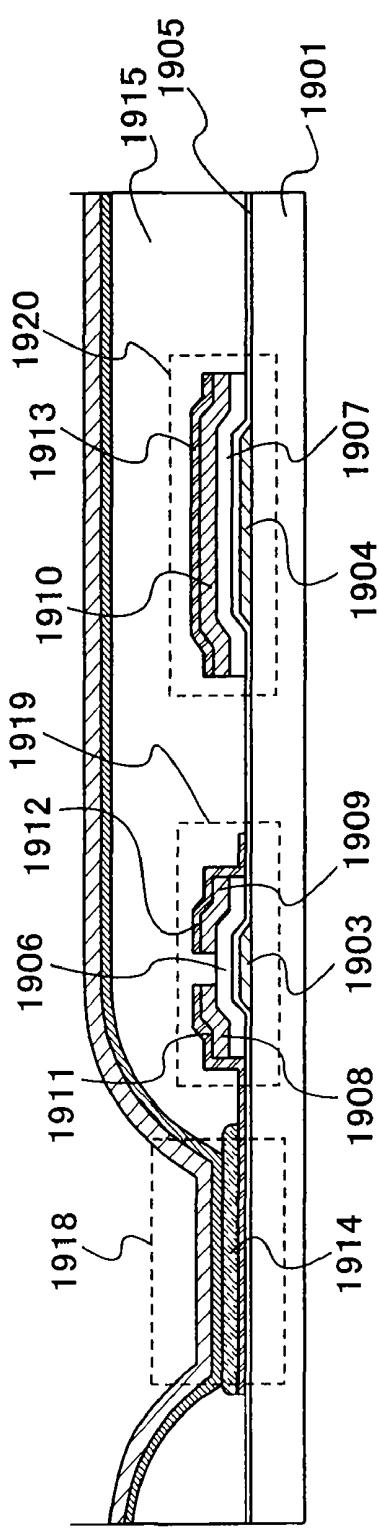

FIG. 19A

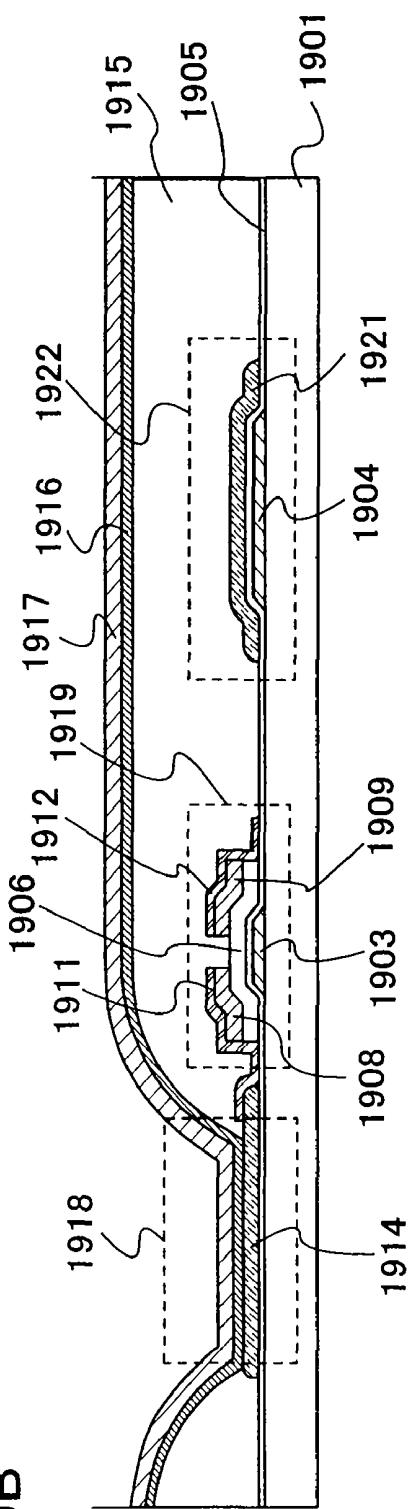

**FIG. 19B**

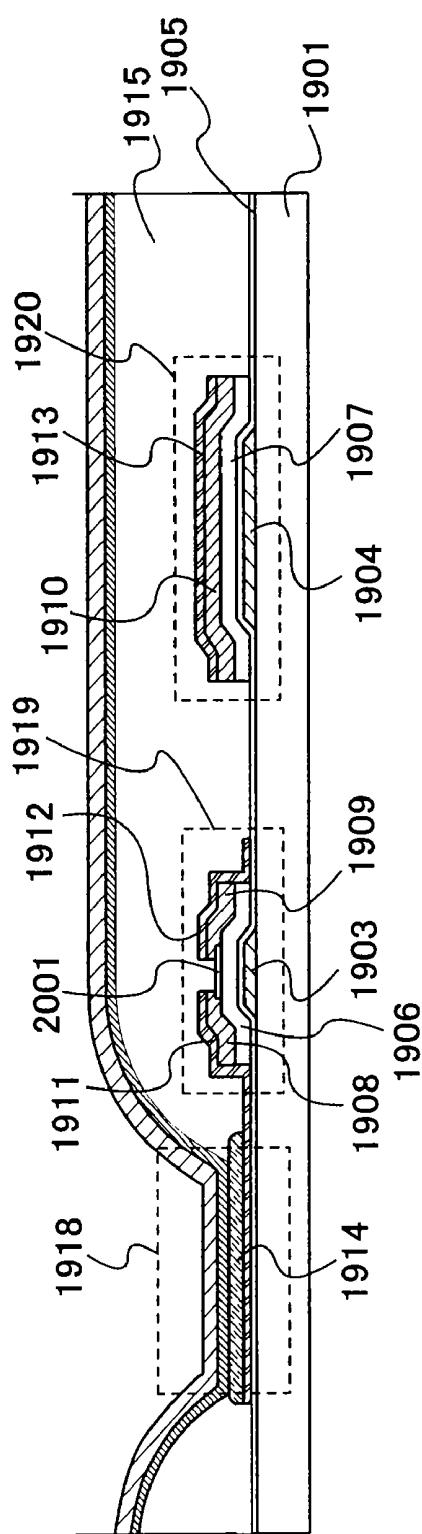

FIG.20A

FIG.20B

FIG.21

FIG.22A

FIG.22B

FIG.22C

FIG.22D

FIG.22E

FIG.23A

FIG.23B

FIG.24A

FIG.24B

FIG.25A

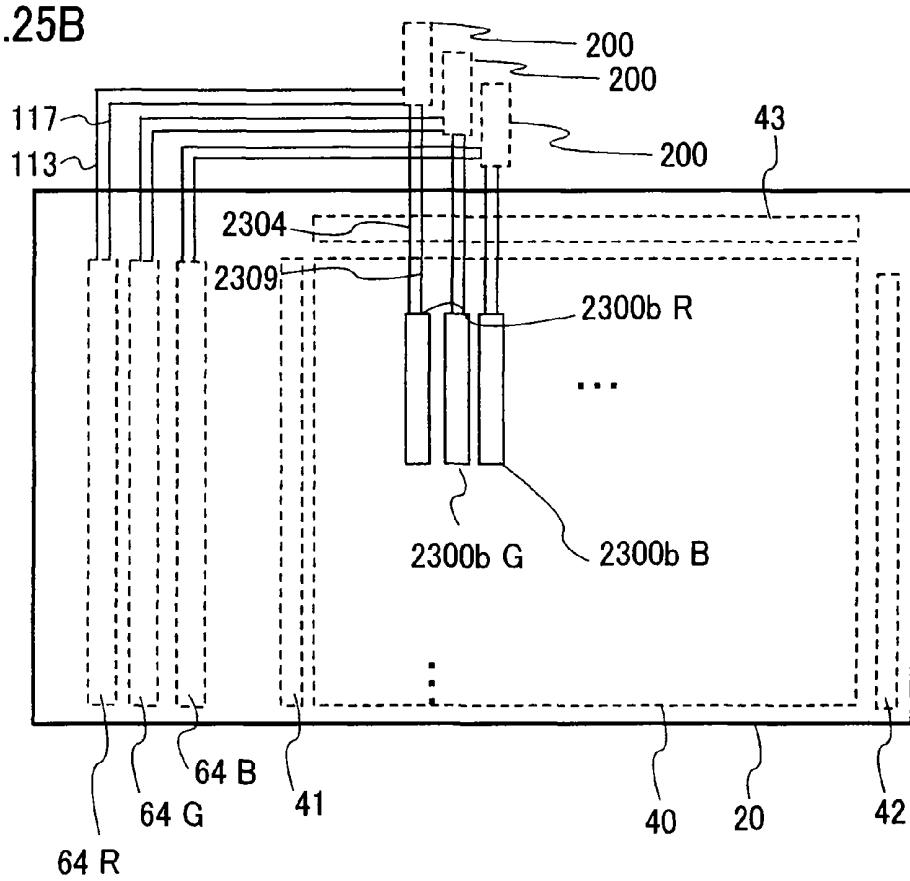

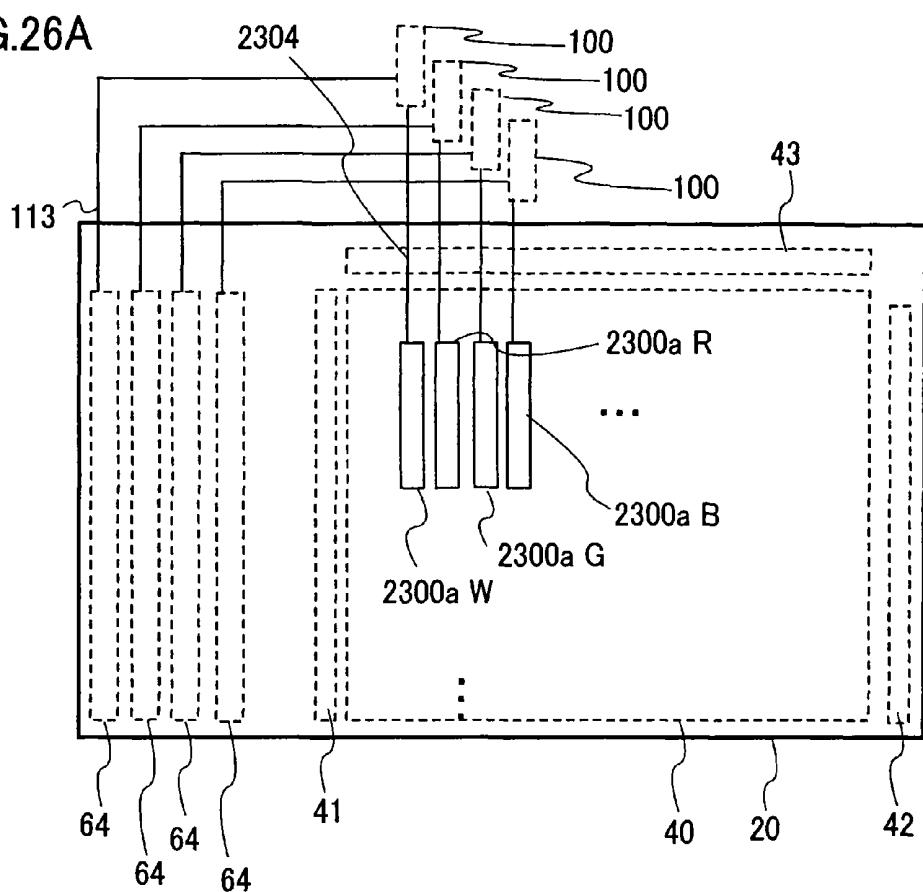

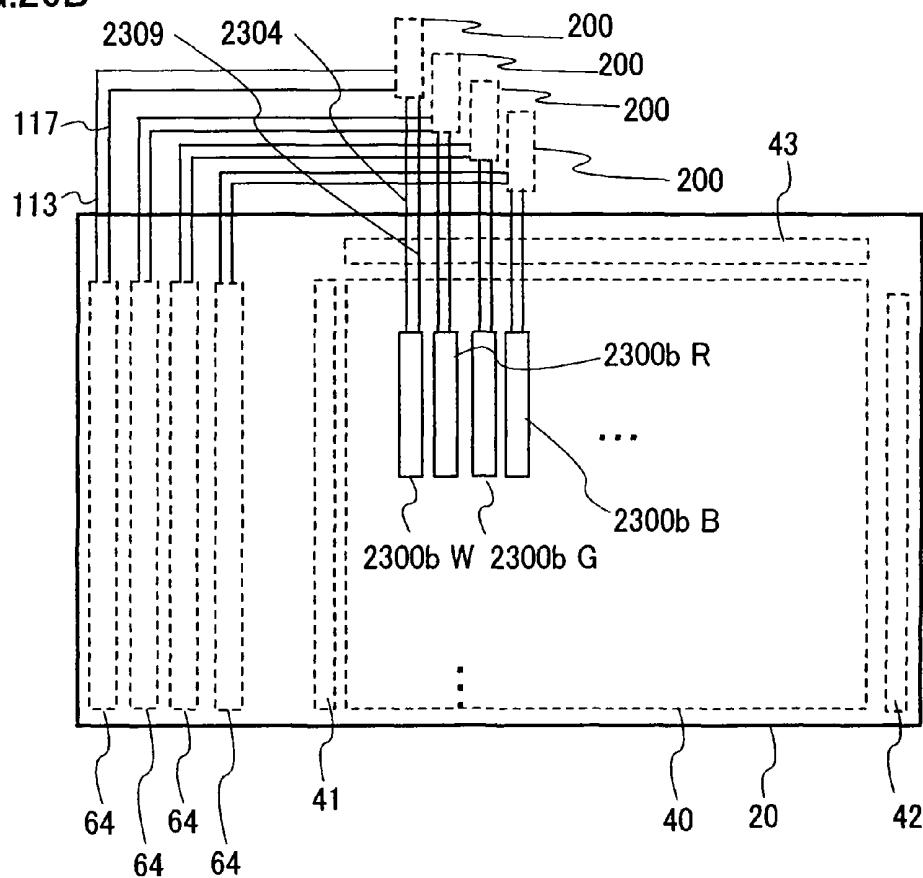

FIG.25B

FIG.26A

FIG.26B

FIG.27

FIG.28

FIG.29

FIG.30

FIG.31

FIG.32

FIG.33

## DISPLAY DEVICE AND DRIVING METHOD THEREOF

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The invention relates to a display device having a pixel including a light emitting element and a driving method thereof.

[0003] 2. Description of the Related Art

[0004] A flat type display device having a pixel including an electroluminescence element (hereinafter also referred to as "a light emitting element") has been developed. This display device is said to have a wider viewing angle than a liquid crystal display device as a light emitting element in a pixel emits light by itself despite that a screen has a flat shape. Further, an advantage of this display device in that it can be thinner and lighter than a liquid crystal display device is attracting attentions.

[0005] In the case where a pixel is formed of a light emitting element, an analog grayscale method to control a current value or a voltage level supplied to the light emitting element is known as a method for controlling the luminance of the pixel (for example, see Patent Document 1). Moreover, a time grayscale method to control light emission time of a light emitting element is known (for example, see Patent Document 2). Besides, an area grayscale method to divide one pixel into a plurality of regions and control a light emission state of each divided pixel is known (for example, see Patent Document 3).

[Patent Document 1]

[0006] Japanese Patent Laid-Open No. 2003-288055

[Patent Document 2]

[0007] Japanese Patent Laid-Open No. 2002-123219

[Patent Document 3]

[0008] Japanese Patent Laid-Open No. 2001-184015

### SUMMARY OF THE INVENTION

[0009] However, a light emitting element has a problem in that its luminance changes by a temperature change or passage of light emission time. Such deterioration of luminance is considered an issue to be solved since it appears notably as deterioration of image quality in a display device which employs an area grayscale method.

[0010] In view of this, the invention improves and stabilizes image quality of a display device which performs area grayscale display by using a light emitting element.

[0011] The point of the invention is that a portion of a display device having a pixel including a light emitting element is provided with a light emitting element having the same configuration as the pixel so as to function as a monitor light emitting element, thereby a voltage or a current supplied to the light emitting element is corrected in consideration of a change of the monitor light emitting element.

[0012] The invention provides a display device including a plurality of monitor light emitting elements, a monitor line for monitoring a change in potential of an electrode included in the plurality of monitor light emitting elements, and a unit

for electrically blocking a current supply to a shorted monitor light emitting element through the monitor line when any of the plurality of monitor light emitting elements is shorted.

[0013] The invention provides a display device having a display pixel including a plurality of subpixels including light emitting elements with approximately the same light emission color, and a monitor pixel with the same configuration as the display pixel. It is preferable that a light emitting element provided in this pixel and a light emitting element provided in the monitor pixel be formed simultaneously in a manufacturing step and have the same configurations. The light emitting element of each of the subpixels in the monitor pixel is connected to different constant current sources. The display device includes a differential amplifier circuit which changes a potential applied to the light emitting element in the display pixel for each subpixel in accordance with a potential change of the light emitting element in the monitor pixel for each subpixel.

[0014] By providing a monitor light emitting element with the same configuration as a light emitting element provided in a pixel, luminance variations caused by a change in an environmental temperature or deterioration with time can be suppressed. As a result, image quality can be improved or stabilized.

### BRIEF DESCRIPTION OF DRAWINGS

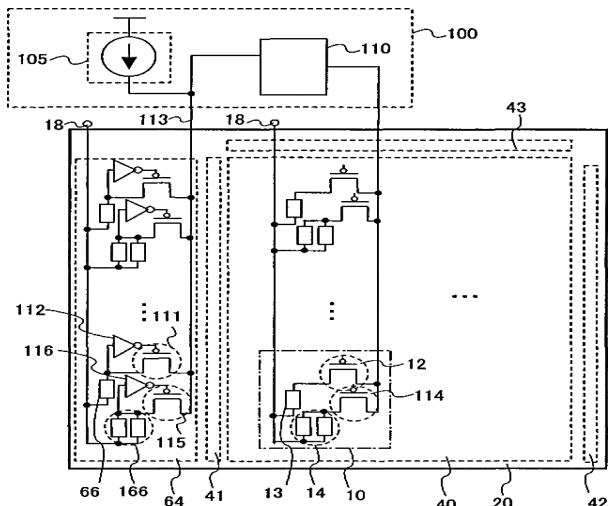

[0015] FIG. 1 is a diagram showing a display device of the invention.

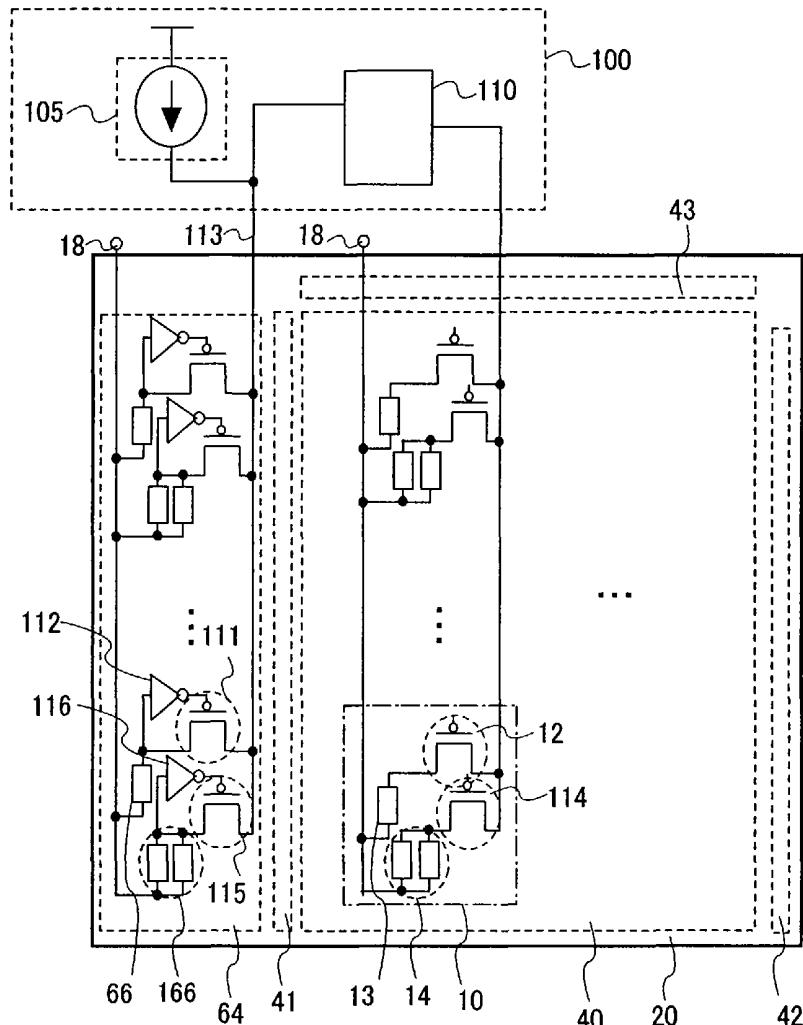

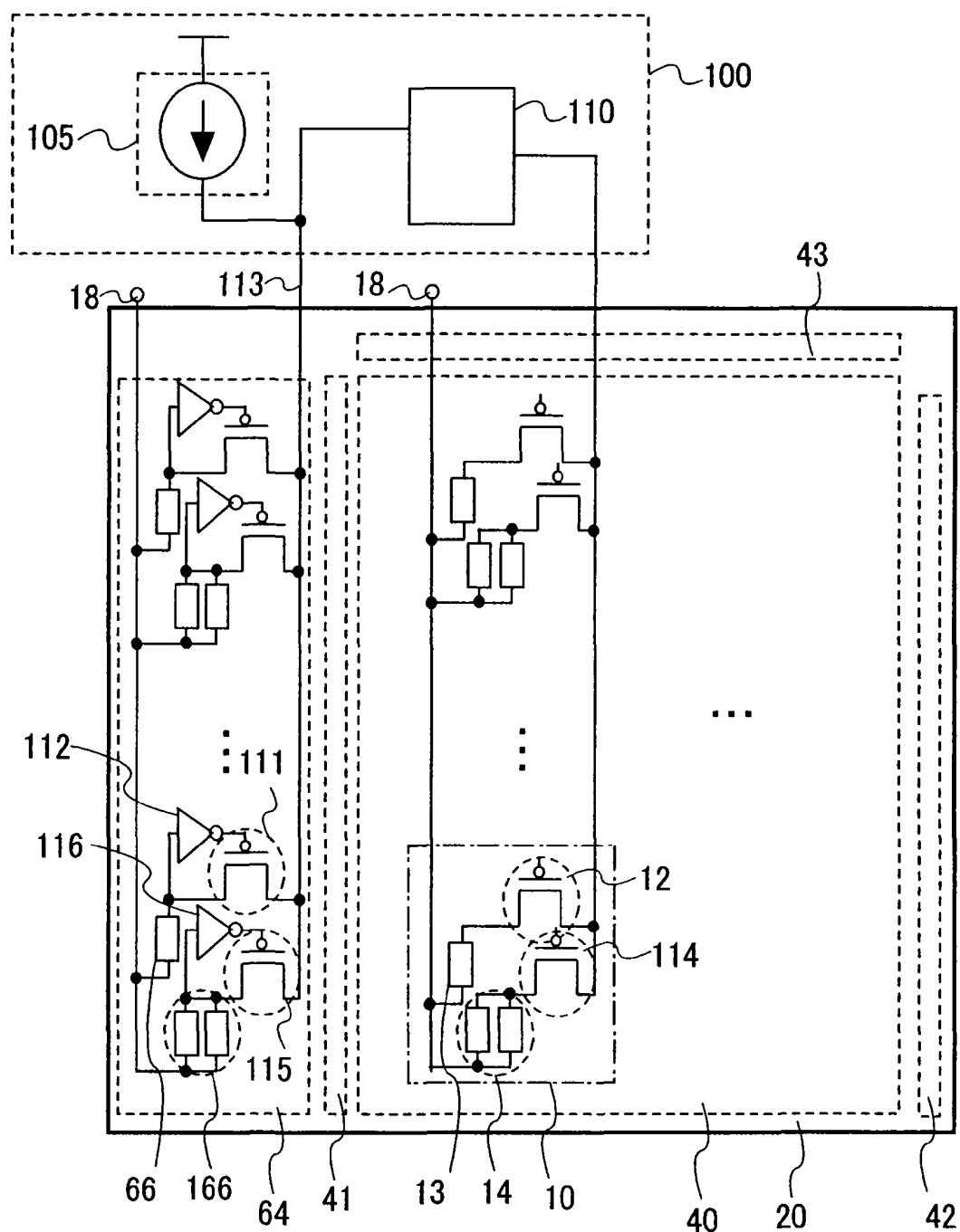

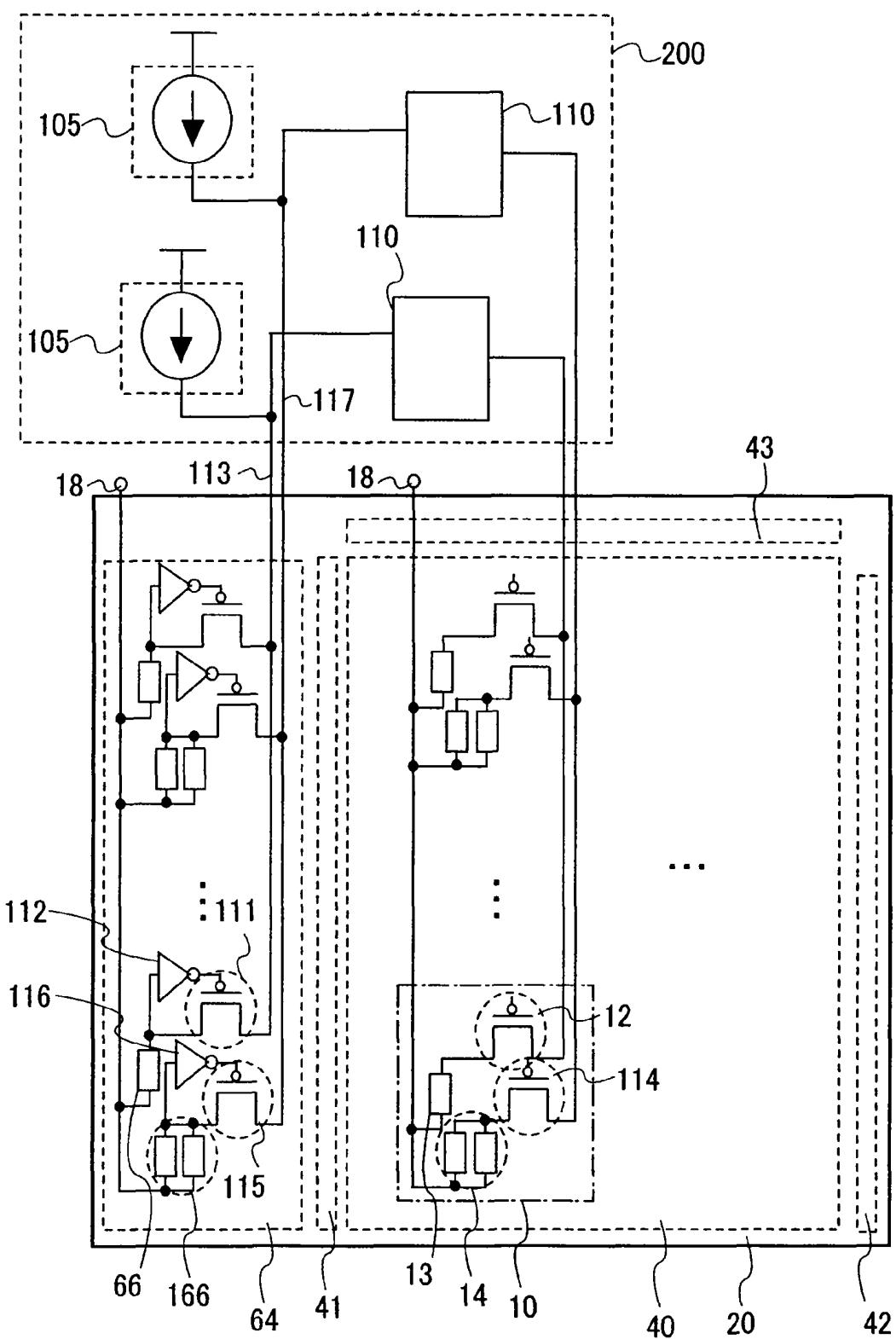

[0016] FIG. 2 is a diagram showing a display device of the invention.

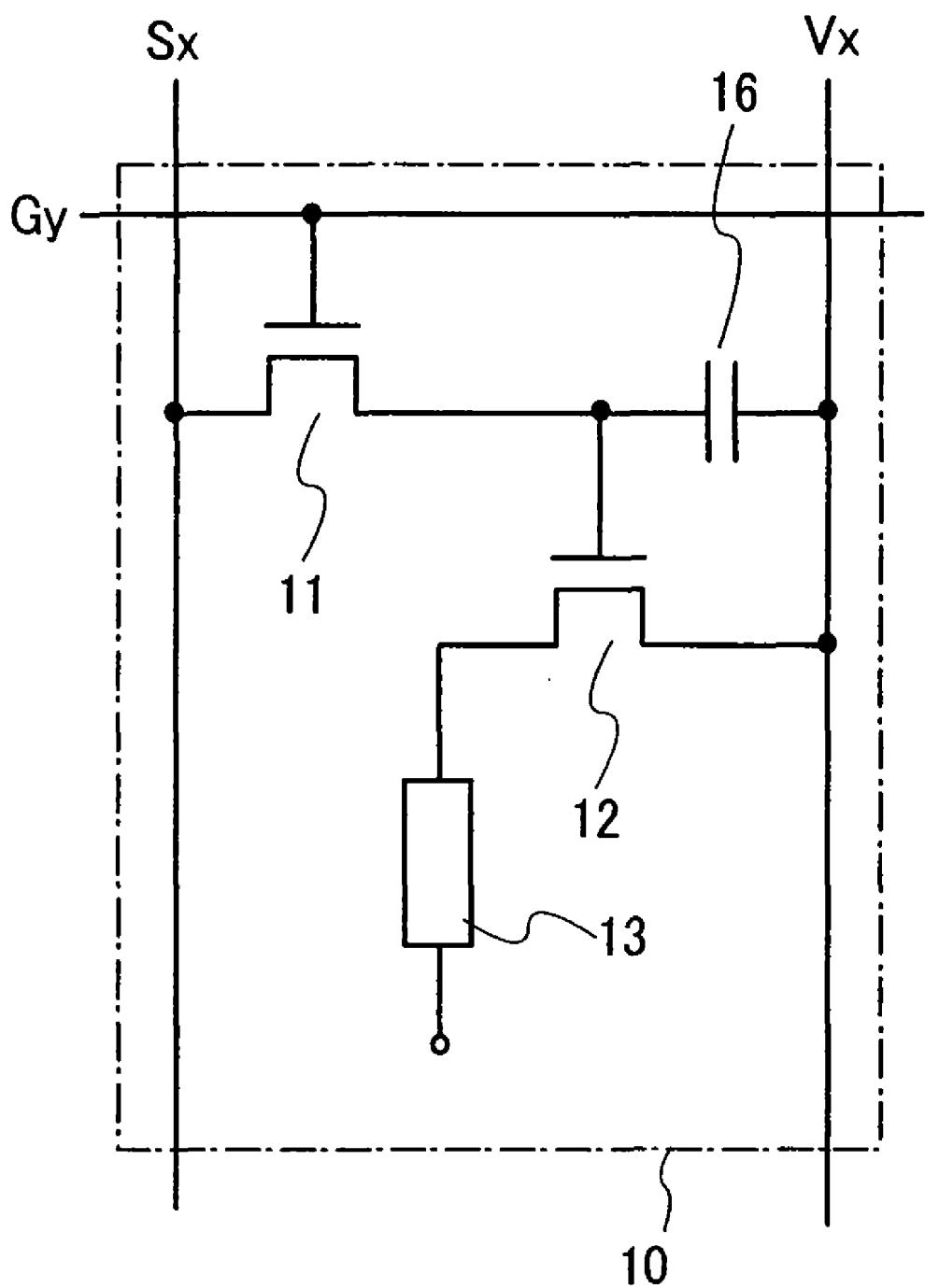

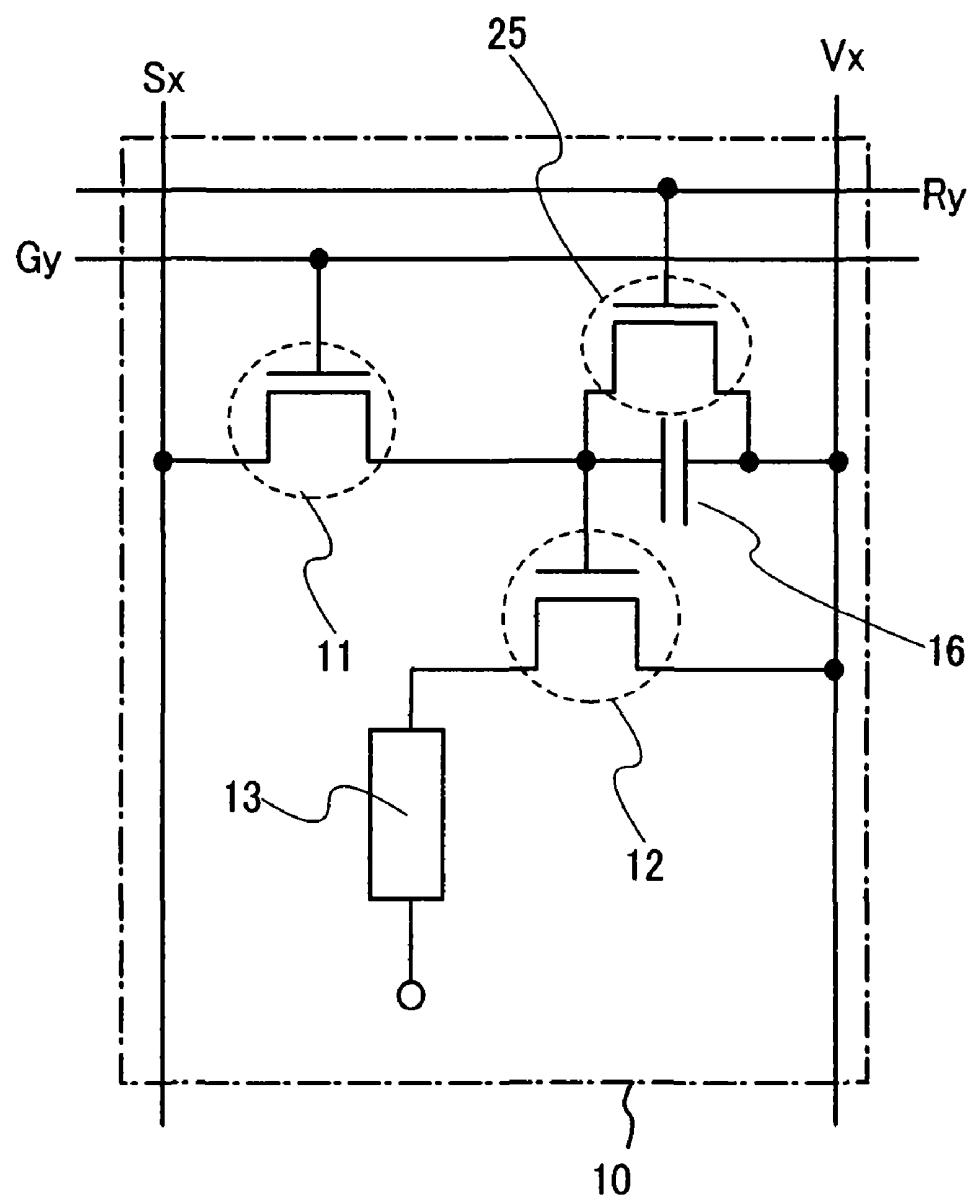

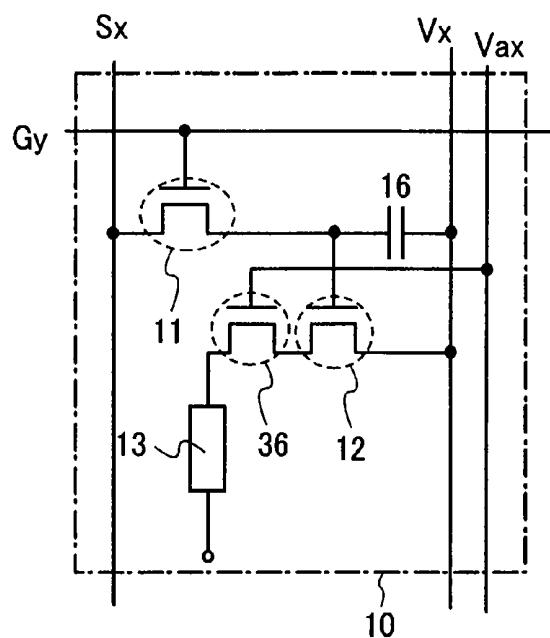

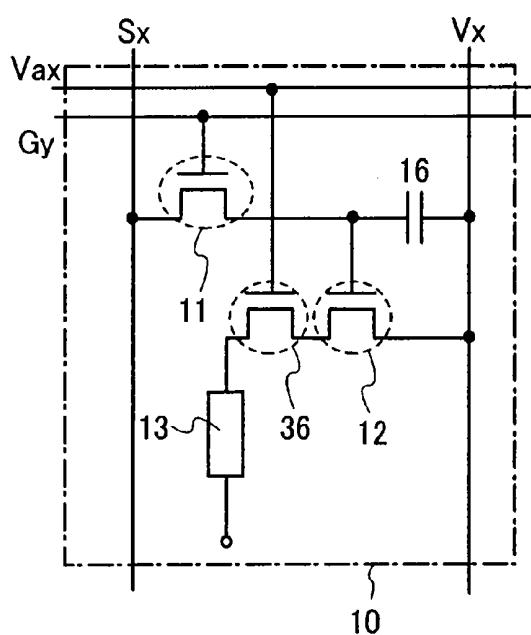

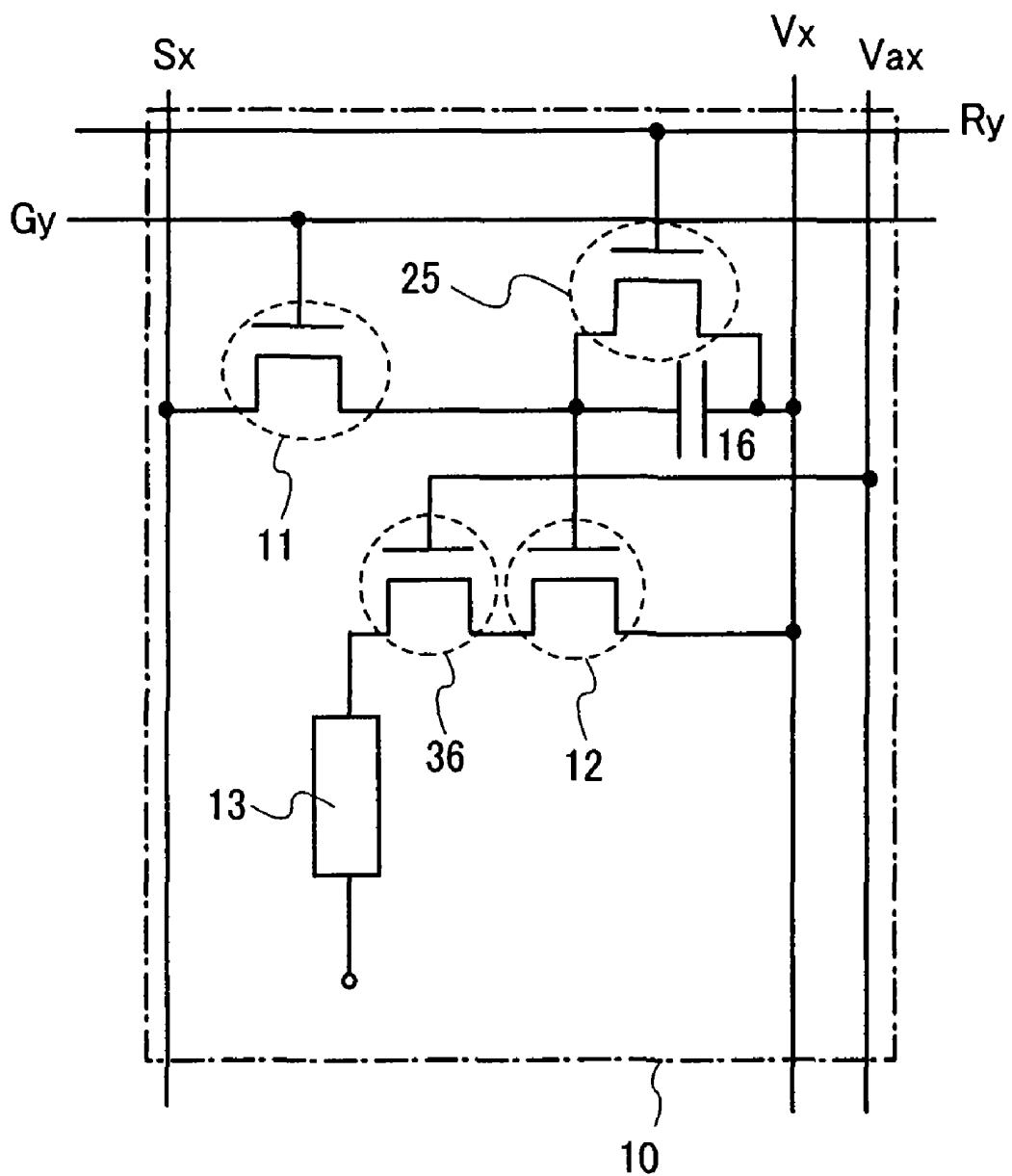

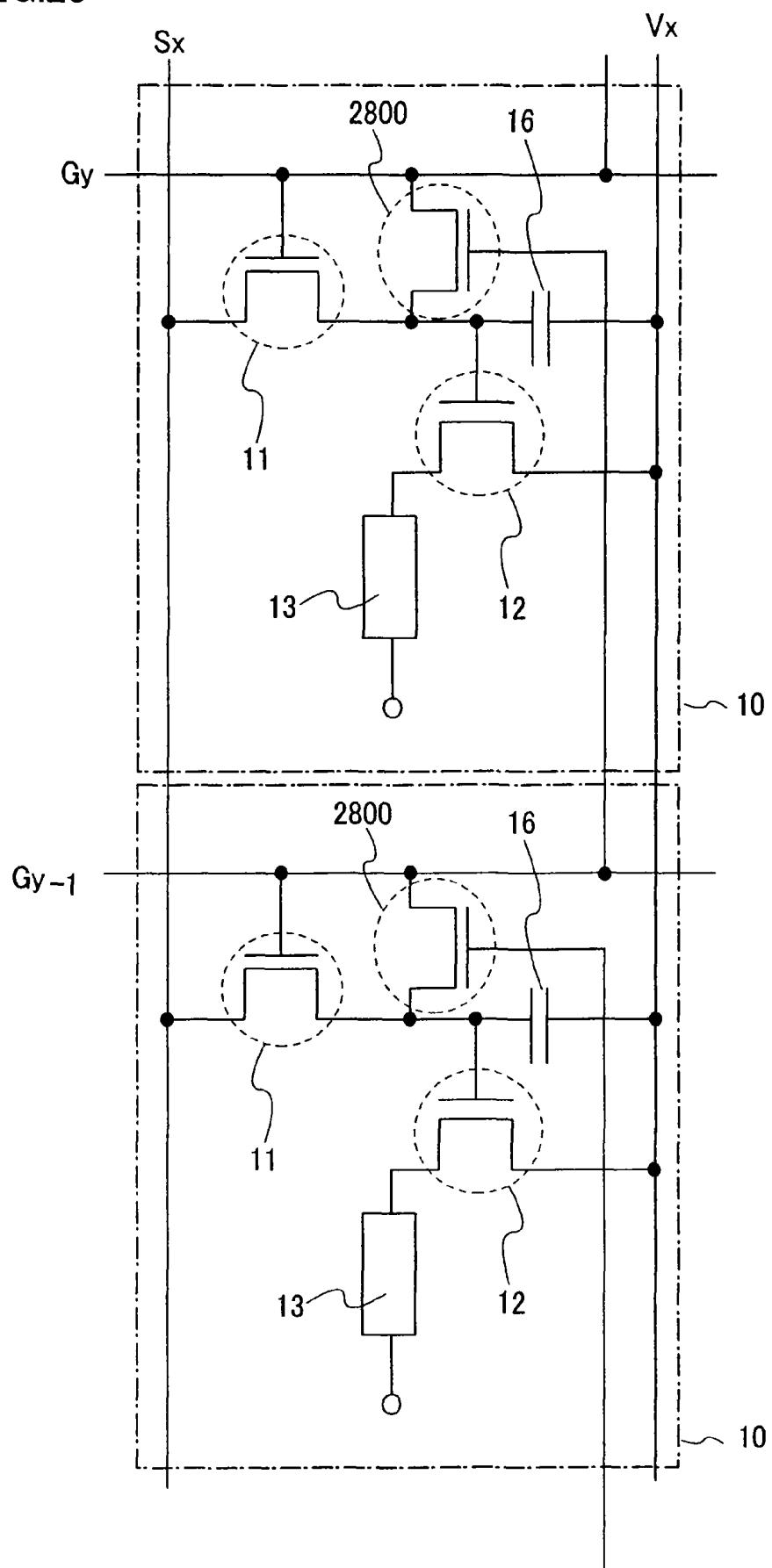

[0017] FIG. 3 is a diagram showing an equivalent circuit of a pixel of the invention.

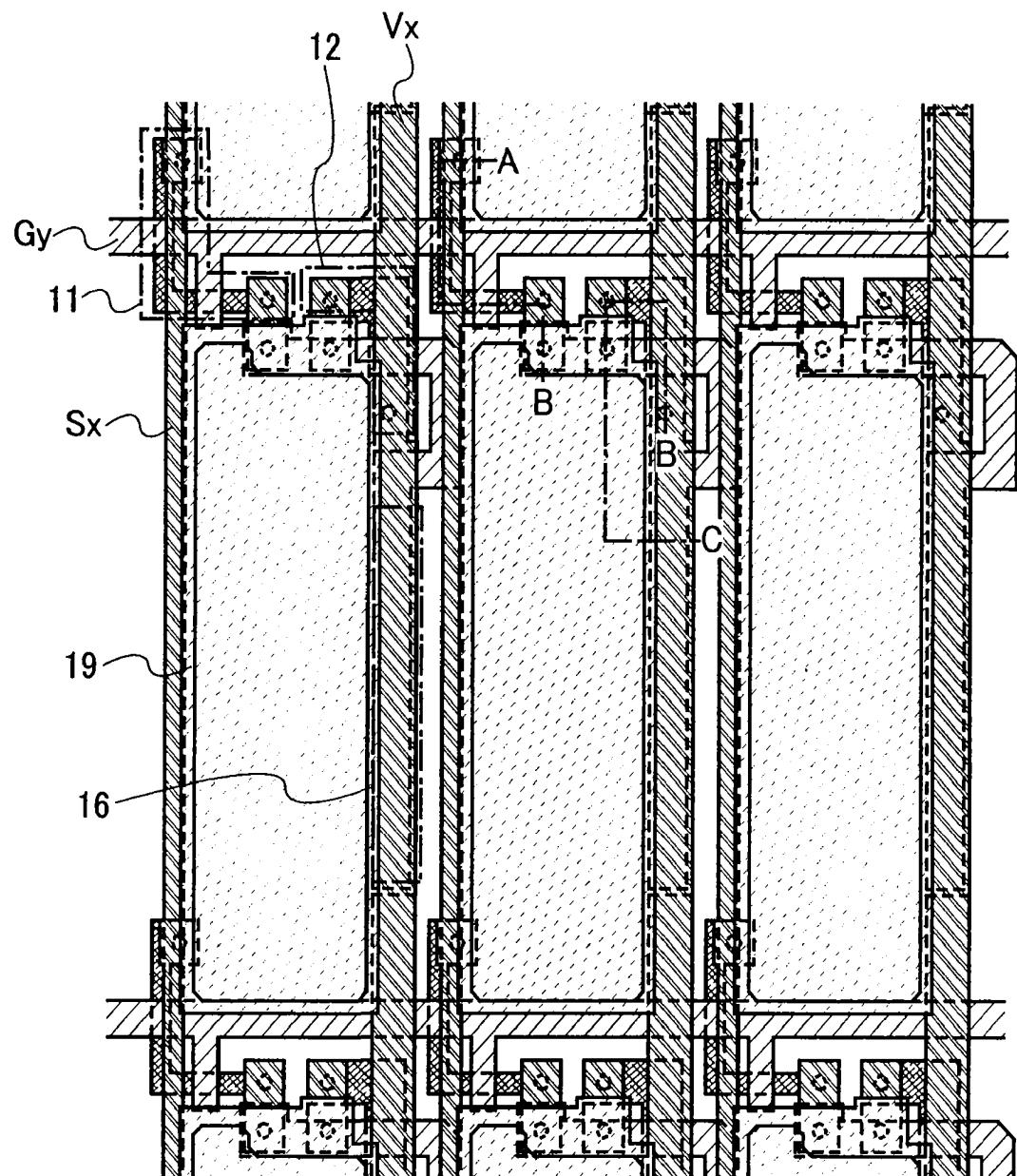

[0018] FIG. 4 is a diagram showing a layout of a pixel of the invention.

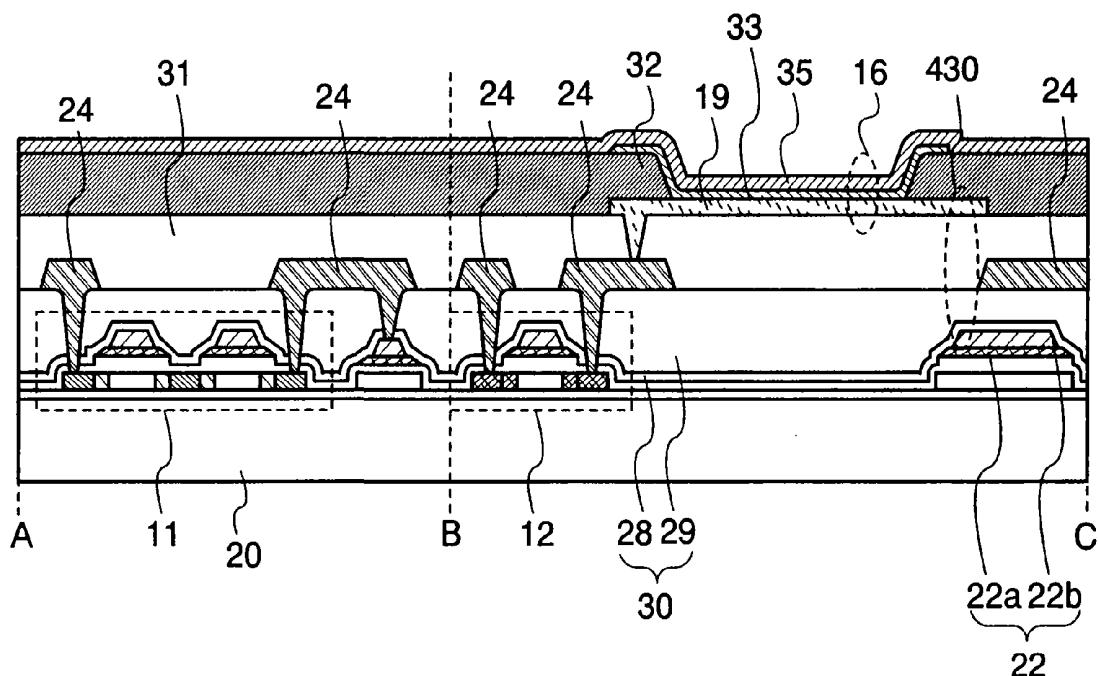

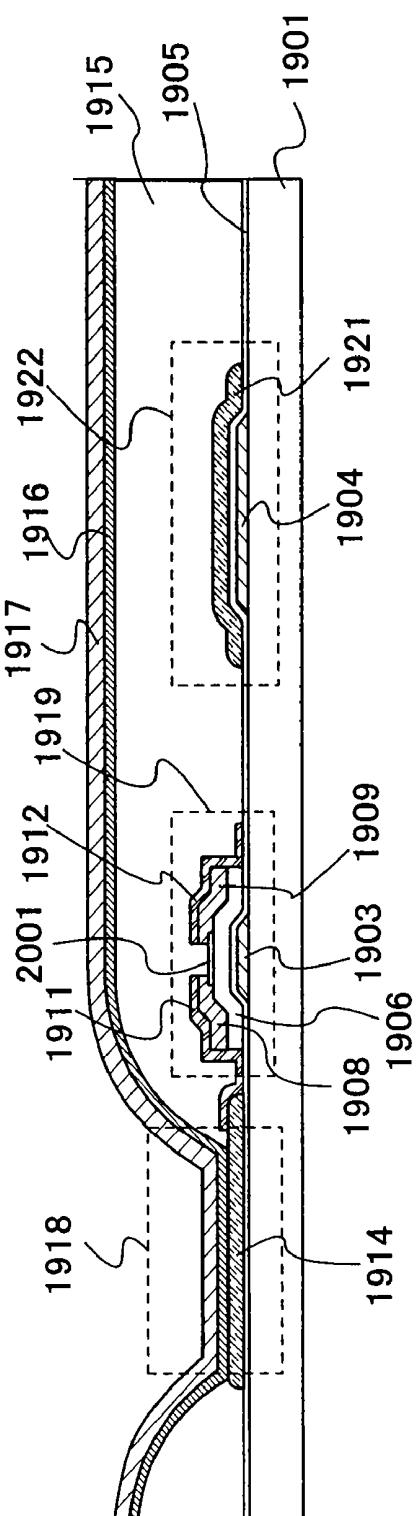

[0019] FIG. 5 is a view showing a cross section of a pixel of the invention.

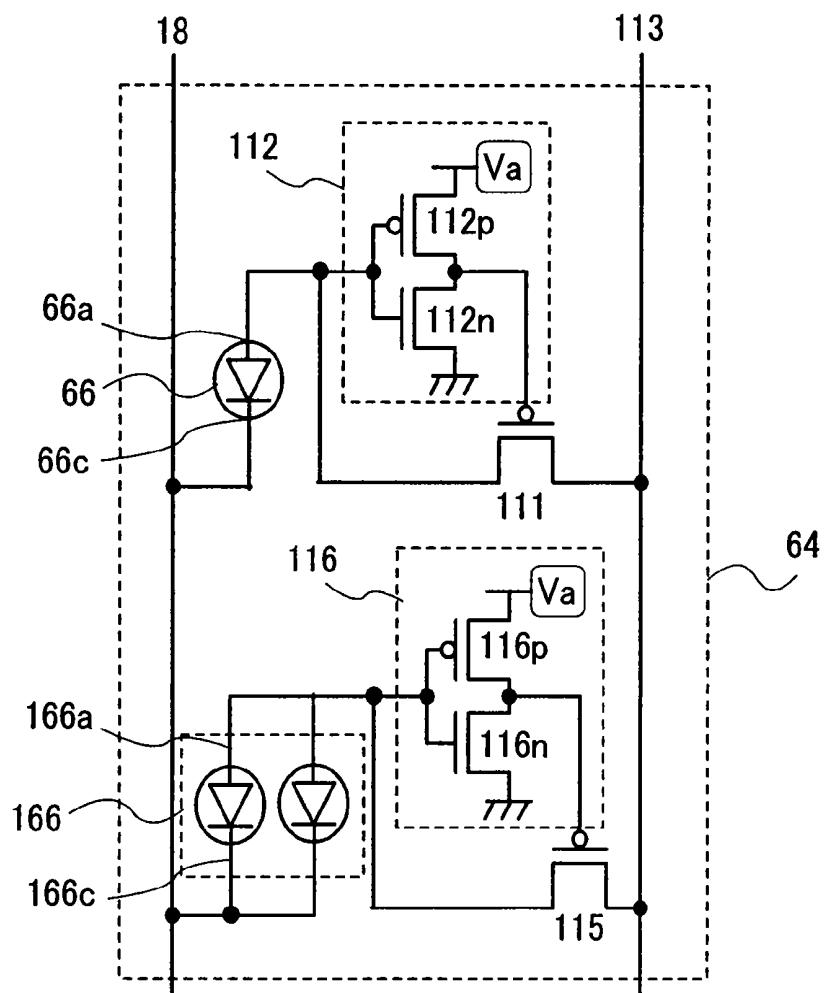

[0020] FIGS. 6A and 6B are views showing a monitor circuit of the invention.

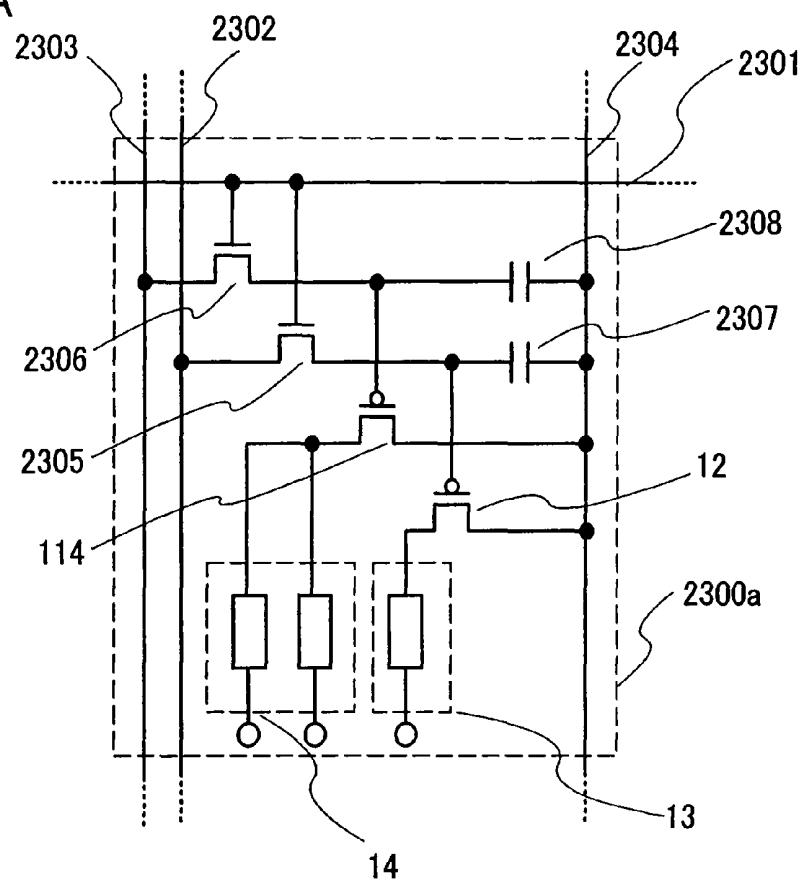

[0021] FIGS. 7A and 7B are views showing a monitor circuit of the invention.

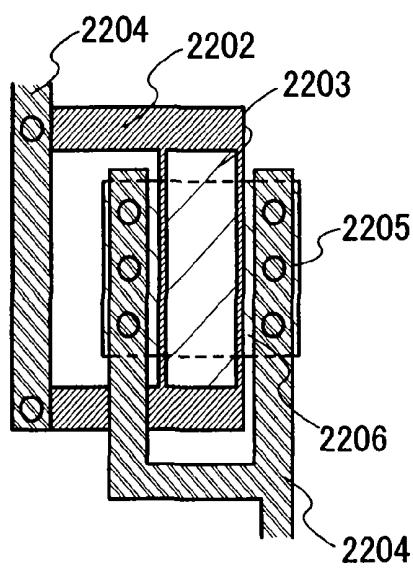

[0022] FIGS. 8A and 8B are views showing a monitor circuit of the invention.

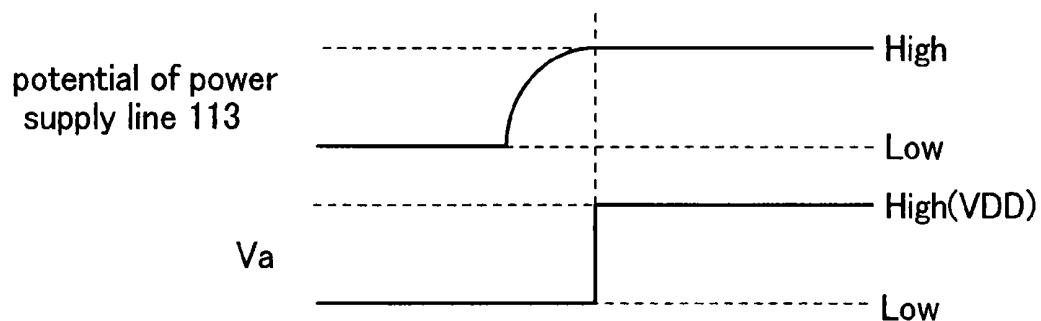

[0023] FIGS. 9A and 9B are timing charts of the invention.

[0024] FIG. 10 is a diagram showing an equivalent circuit of a pixel of the invention.

[0025] FIGS. 11A to 11C are diagrams showing equivalent circuits of a pixel of the invention.

[0026] FIG. 12 is a diagram showing an equivalent circuit of a pixel of the invention.

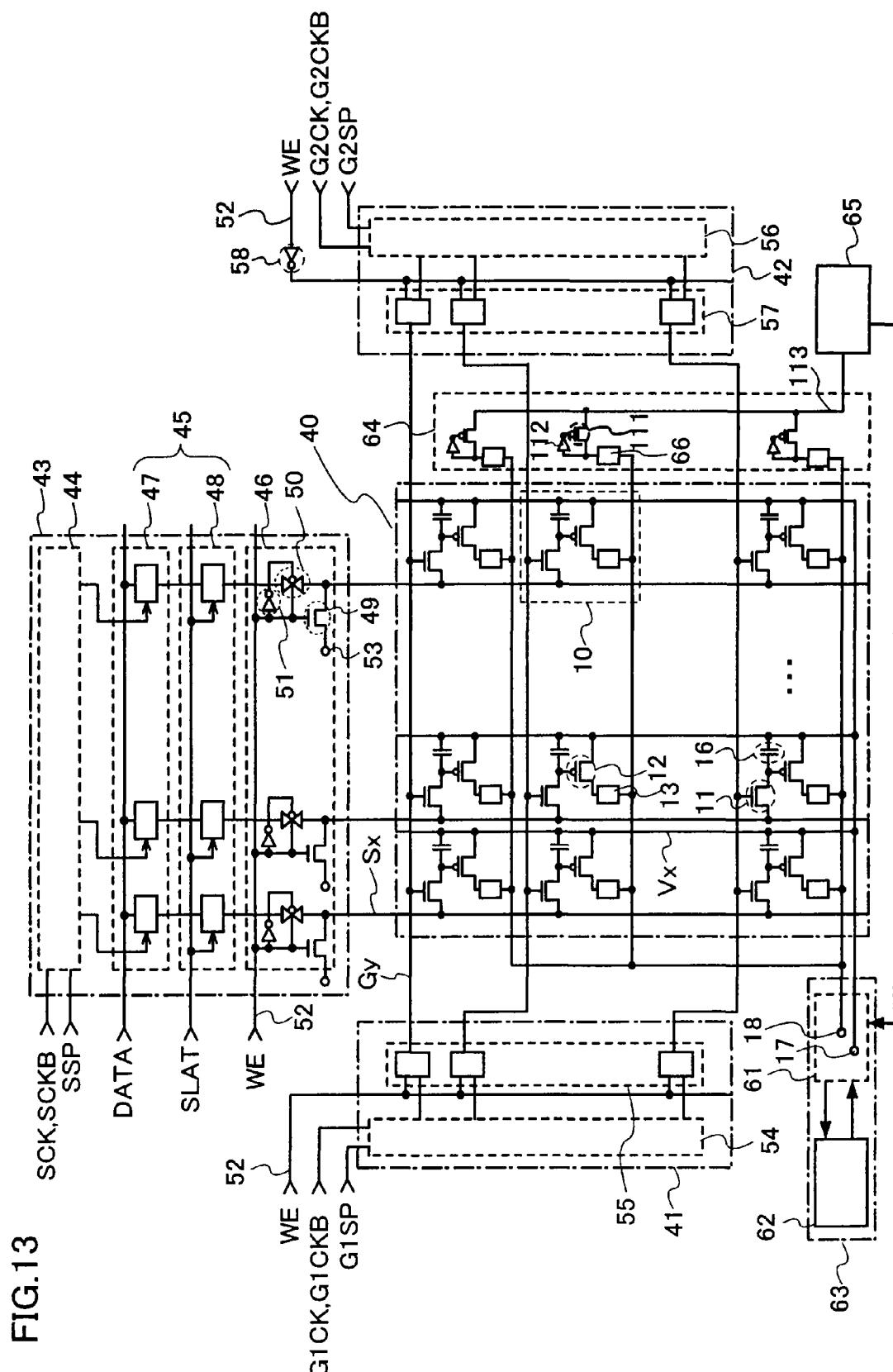

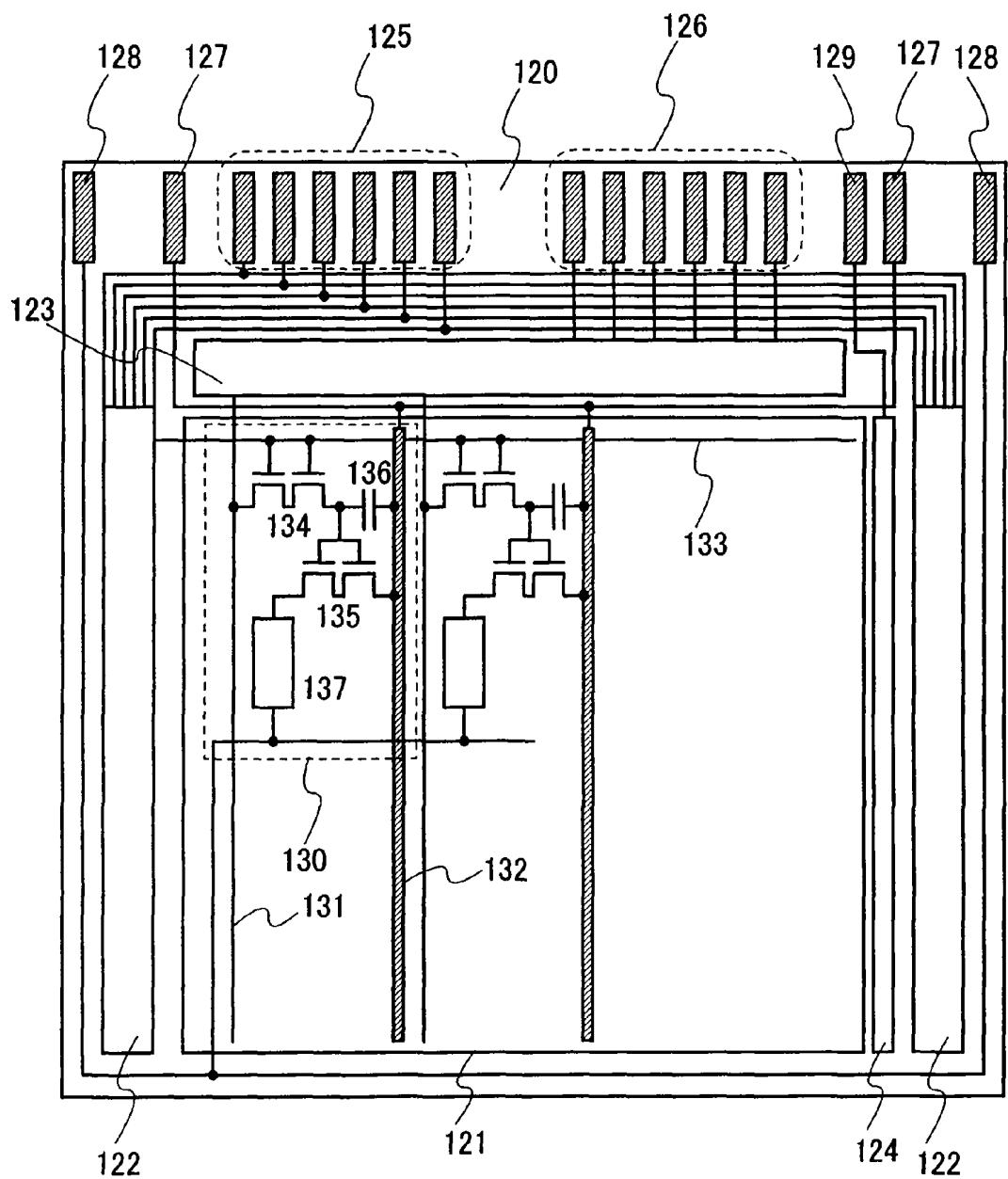

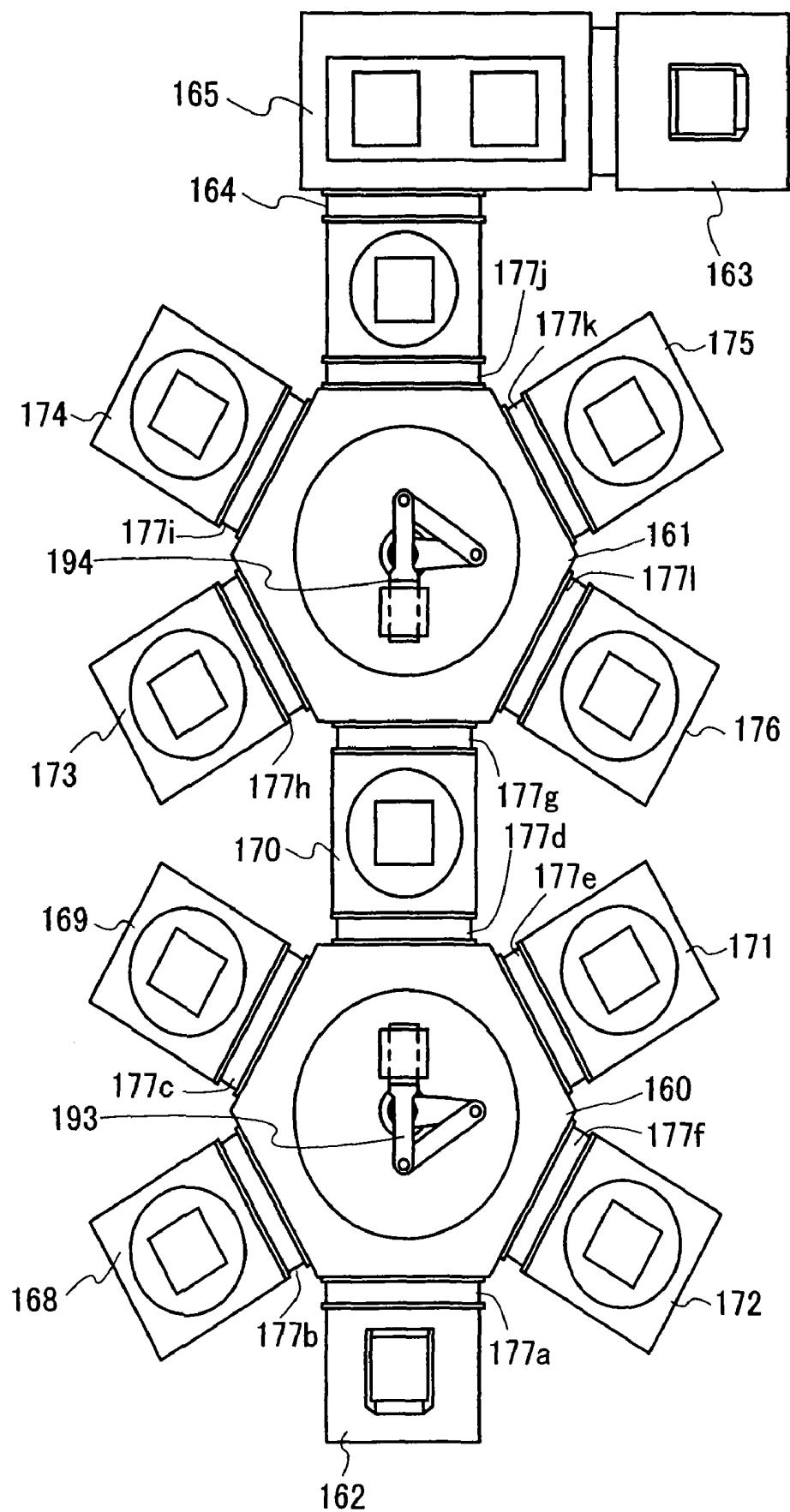

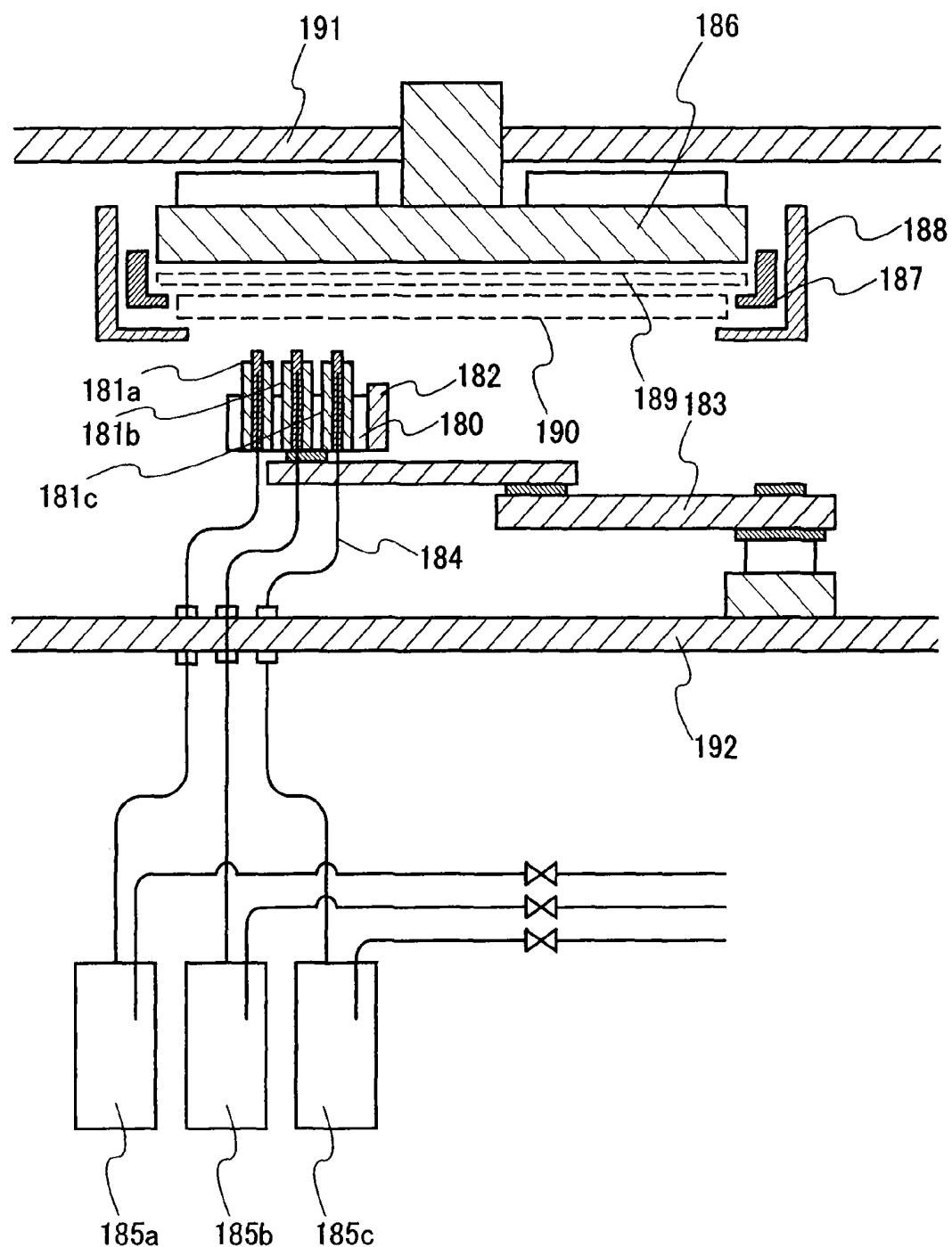

[0027] FIG. 13 is a diagram showing a panel of the invention.

[0028] FIG. 14 is a timing chart of the invention.

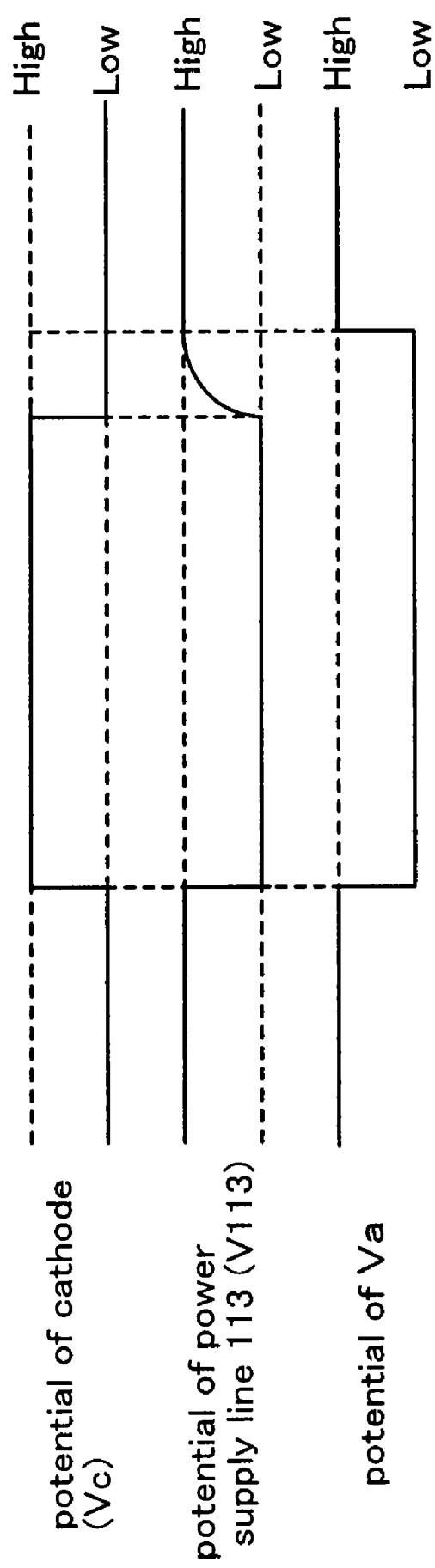

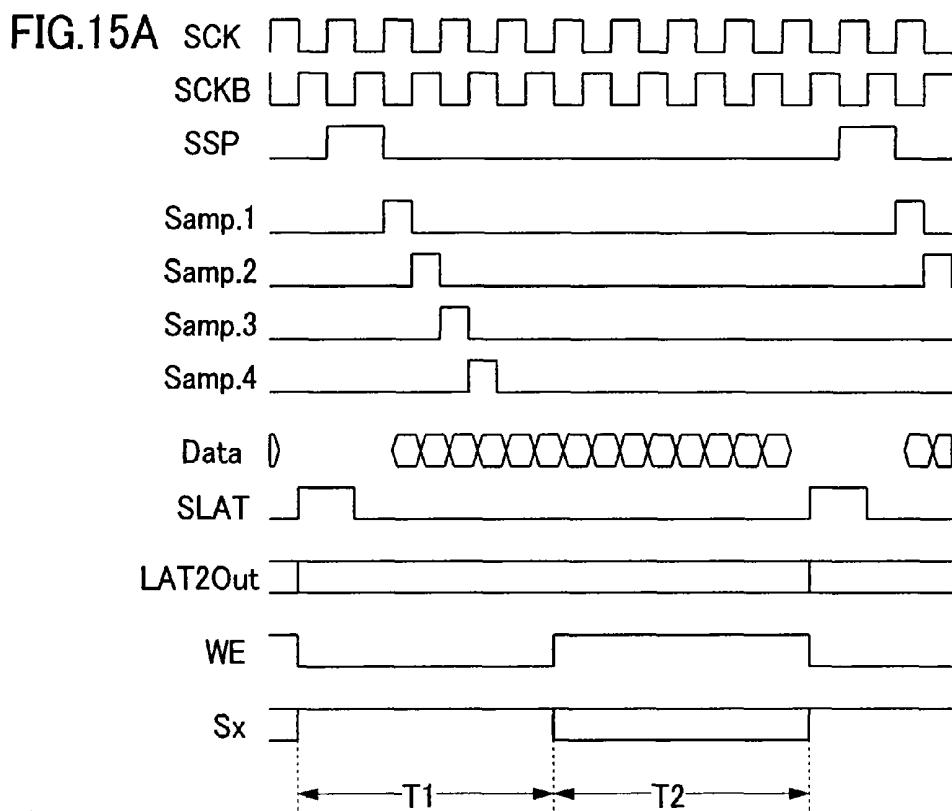

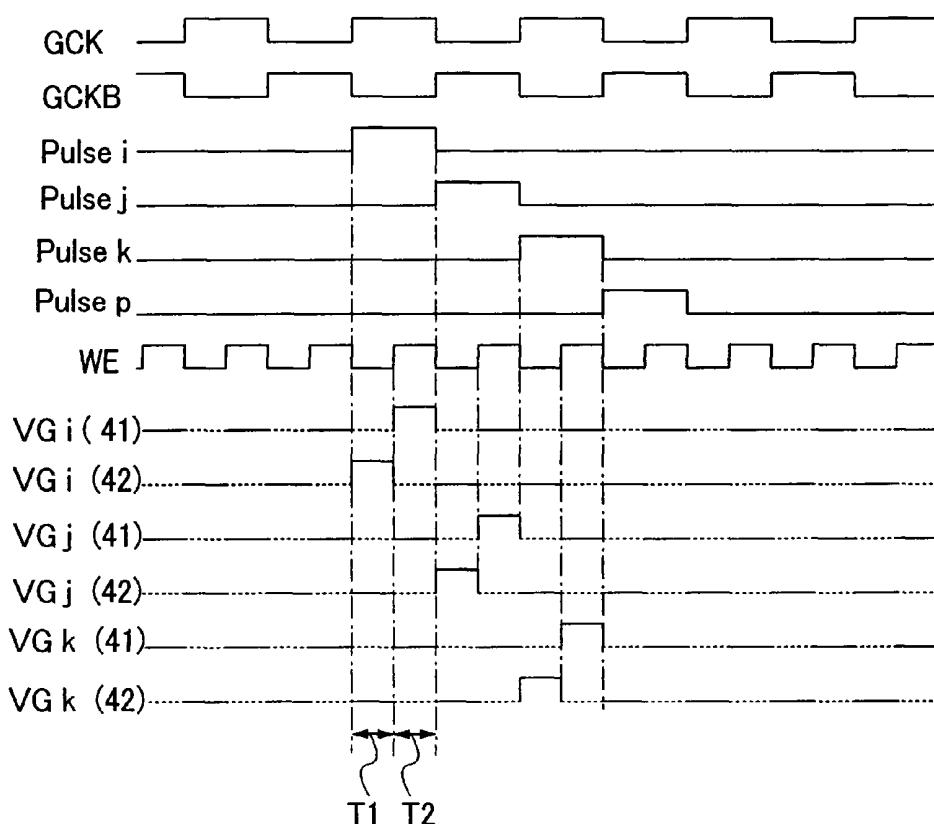

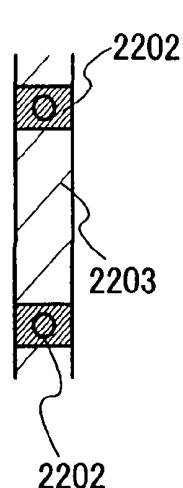

[0029] FIGS. 15A and 15B are timing charts of the invention.

[0030] FIGS. 16A to 16F are views showing electronic devices of the invention.

[0031] FIGS. 17A to 17C are views showing examples of a display device to which the invention can be applied.

[0032] FIGS. 18A and 18B are views showing examples of a display device to which the invention can be applied.

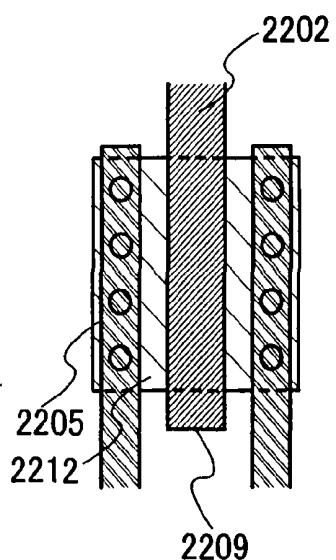

[0033] FIGS. 19A and 19B are views showing examples of a display device to which the invention can be applied.

[0034] FIGS. 20A and 20B are views showing examples of a display device to which the invention can be applied.

[0035] FIG. 21 is a view showing an example of a display device to which the invention can be applied.

[0036] FIGS. 22A to 22E are views showing examples of a display device to which the invention can be applied.

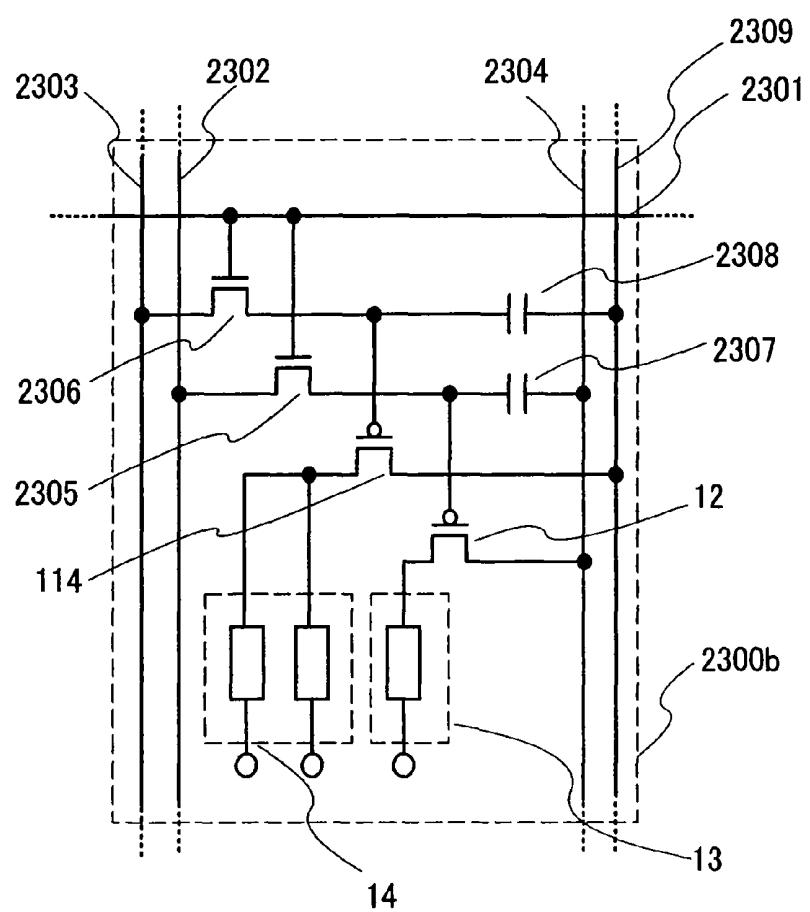

[0037] FIGS. 23A and 23B are diagrams showing equivalent circuits of a pixel of the invention.

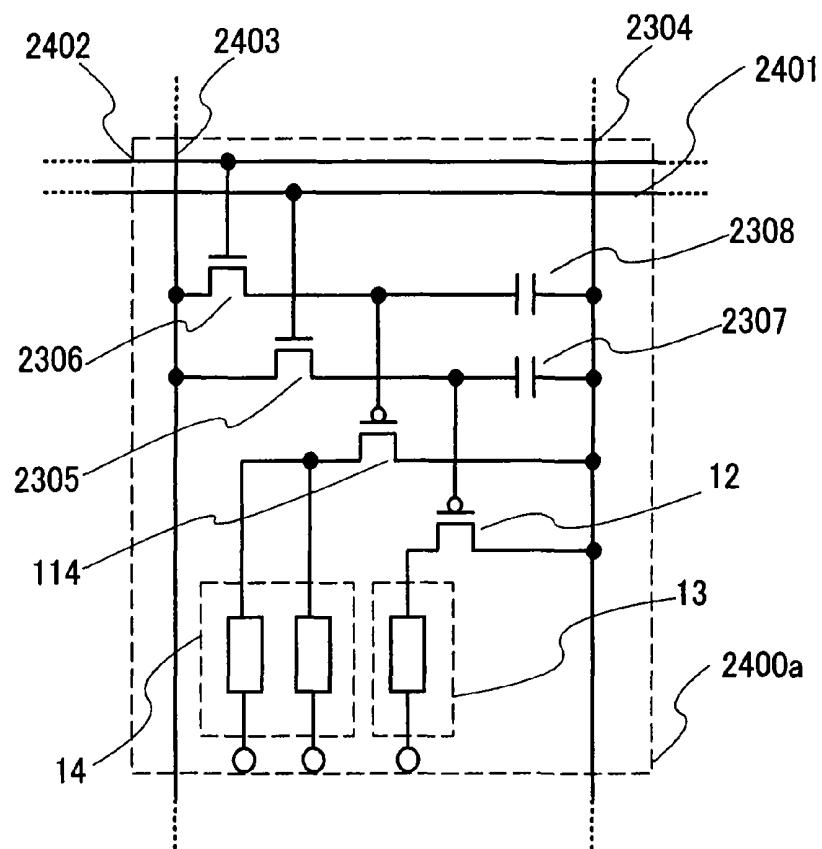

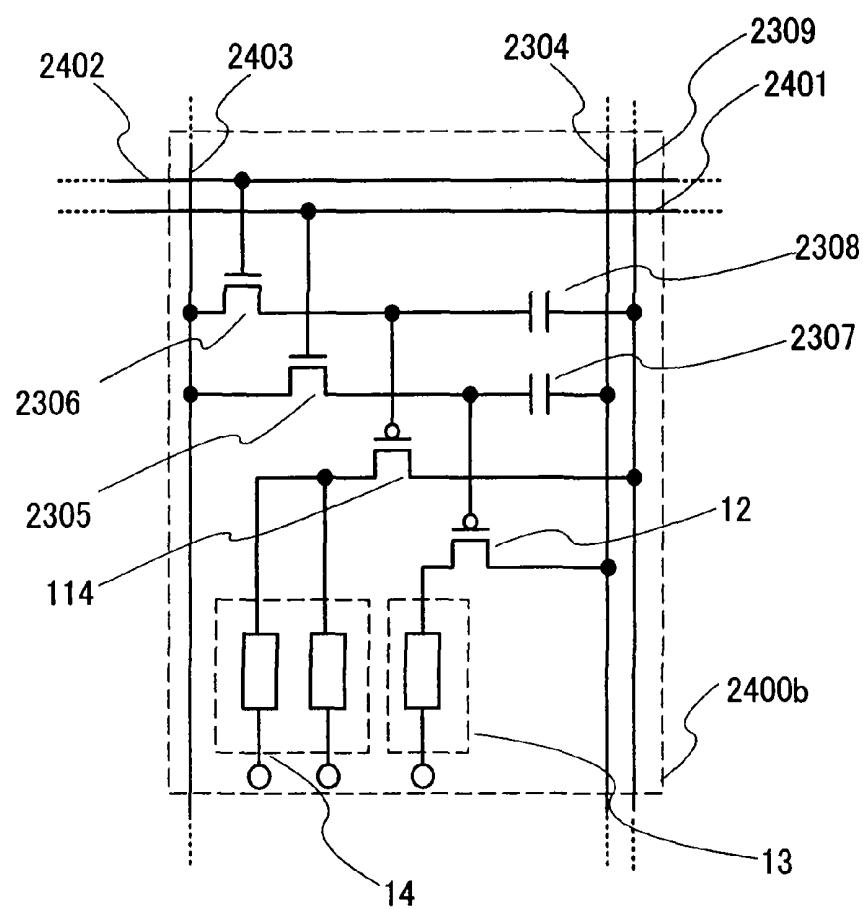

[0038] FIGS. 24A and 24B are diagrams showing equivalent circuits of a pixel of the invention.

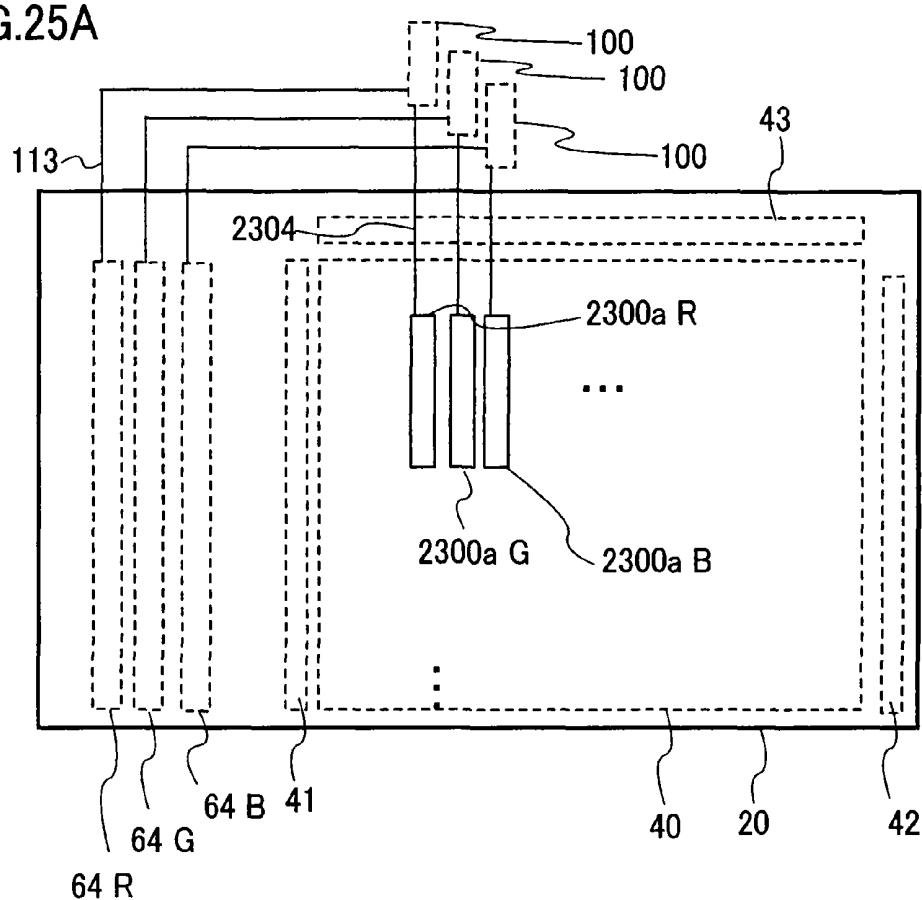

[0039] FIGS. 25A and 25B are diagrams showing a display device of the invention.

[0040] FIGS. 26A and 26B are diagrams showing a display device of the invention.

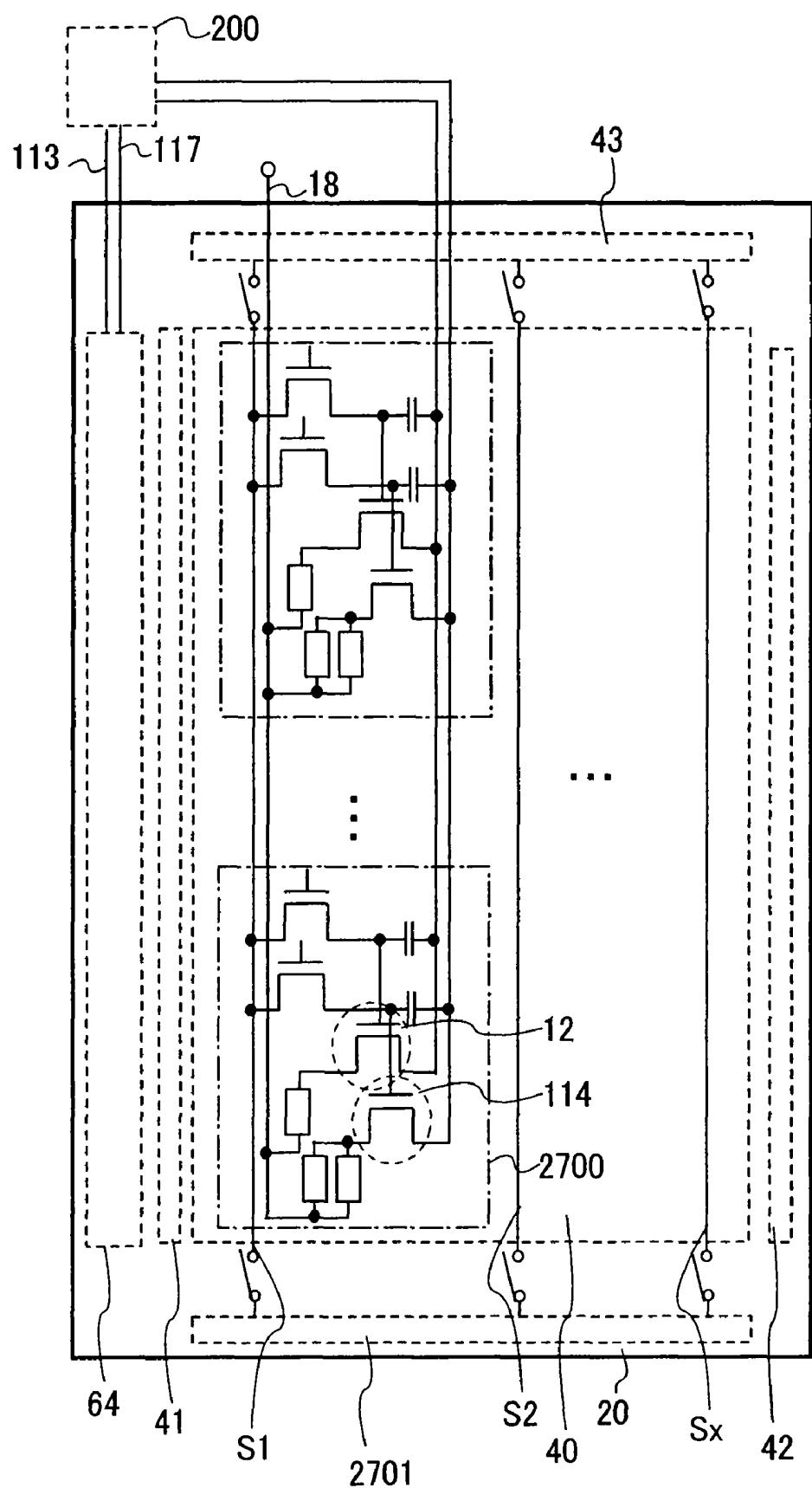

[0041] FIG. 27 is a diagram showing a display device of the invention.

[0042] FIG. 28 is a diagram showing a suitable pixel configuration for applying a negative voltage to a gate of a driving transistor.

[0043] FIG. 29 is a diagram showing a configuration of a display panel of the invention.

[0044] FIG. 30 is a diagram showing a configuration of a subpixel in a display panel of the invention.

[0045] FIG. 31 is a diagram showing a configuration of a subpixel in a display panel of the invention.

[0046] FIG. 32 is a diagram showing a structure of a vapor deposition apparatus for forming an EL layer.

[0047] FIG. 33 is a diagram showing a structure of a vapor deposition apparatus for forming an EL layer.

#### DETAILED DESCRIPTION OF THE INVENTION

[0048] Although the present invention will be fully described by way of embodiment modes with reference to the accompanying drawings, it is to be understood that various changes and modifications will be apparent to those skilled in the art. Therefore, unless such changes and modifications depart from the scope of the invention, they should be construed as being included therein. Note that identical portions in embodiment modes are denoted by the same reference numerals and detailed descriptions thereof are omitted.

[0049] It is to be noted in the specification that connected elements are electrically connected. Therefore, connected elements may have a semiconductor element, a switching element, or the like between them.

[0050] In this specification, a source electrode and a drain electrode of a transistor are thus called for convenience in order to distinguish electrodes other than a gate electrode in the configuration of the transistor. In the invention, in the case where the conductivity of a transistor is not limited, the source electrode and the drain electrode are changed in name depending on the conductivity of the transistor. Therefore, a source electrode or a drain electrode is described as one electrode or the other electrode in some cases.

#### Embodiment Mode 1

[0051] In this embodiment mode, a configuration of a panel including a monitor light emitting element is described with reference to the drawings.

[0052] FIG. 1 shows a configuration of a panel including a pixel portion 40, a signal line driver circuit 43, a first scan line driver circuit 41, a second scan line driver circuit 42, and a monitor circuit 64. This panel is formed using an insulating substrate 20.

[0053] The pixel portion 40 includes a plurality of pixels 10. Each pixel includes a first light emitting element 13 and a first driving transistor 12 which is connected to the first light emitting element 13 and has a function to control a current supply. The first light emitting element 13 is connected to a power source 18. Moreover, each pixel may include a second driving transistor 114 and a second light emitting element 14 which are connected in the same way as the first driving transistor 12 and the first light emitting element 13. The second driving transistor 114 and the second light emitting element 14 may be connected in parallel to the first driving transistor 12 and the first light emitting element 13 with a common power source. Here, the second light emitting element 14 may have a configuration in which two light emitting elements with equivalent or almost equivalent functions to the first light emitting element are connected in parallel as shown in FIG. 1. However, the invention is not limited to this and one light emitting element may be provided such as the first light emitting element 13. Further, a plurality of light emitting elements of three or more may be connected in parallel or the functions of the plurality of light emitting elements may not be equivalent to one another. For example, the light emitting element as the second light emitting element 14 may have a different light emission area from that of the first light emitting element 13. That is to say, it is required in one pixel that the second driving transistor 114 and the second light emitting element 14 are connected in parallel to the first driving transistor 12 and the first light emitting element 13. It is to be noted that a more specific configuration of the pixel 10 is described in the following embodiment mode as an example.

[0054] The monitor circuit 64 includes a first monitor light emitting element 66, a first monitor controlling transistor 111 connected to the first monitor light emitting element 66, and a first inverter 112. The first inverter 112 has an output terminal connected to a gate electrode of the first monitor controlling transistor 111. An input terminal of the first inverter 112 is connected to one of a source electrode and a drain electrode of the first monitor controlling transistor 111 and to the first monitor light emitting element 66. A constant current source 105 is connected to the first monitor controlling transistor 111 through a power supply line 113. Other

monitor controlling transistors in the monitor circuit 64 each has a function to control a current supply from the power supply line 113 to each of a plurality of monitor light emitting elements. The power supply line 113 which is connected to electrodes of the plurality of monitor light emitting elements can have a function to monitor a change in potential of the electrodes. Moreover, the constant current source 105 is only required to have a function to supply a constant current to the power supply line 113. Further, the monitor circuit 64 may have a second monitor controlling transistor 115, a second monitor light emitting element 166 and a second inverter 116 which are connected in parallel to the first monitor controlling transistor 111, the first monitor light emitting element 66 and the first inverter 112, with a common power source similarly to the pixel 10.

[0055] The first monitor light emitting element 66 is formed in the same step with the same conditions so as to have the same configuration as the first light emitting element 13. Therefore, the first monitor light emitting element 66 and the first light emitting element 13 have the same or almost the same characteristics against a change in an environmental temperature and deterioration with time. The first monitor light emitting element 66 is connected to the power source 18. Here, the power source connected to the first light emitting element 13 and the power source connected to the first monitor light emitting element 66 have the same potentials; therefore, they are expressed as the power source 18 with the same reference numeral. It is to be noted in this embodiment mode that the first monitor controlling transistor 111 has p-channel conductivity, however, the invention is not limited to this and the first monitor controlling transistor 111 may have an n-channel conductivity as well. In that case, a circuit configuration in the periphery is appropriately changed.

[0056] The second monitor light emitting element 166, the second monitor controlling transistor 115, and the second inverter 116 are similar to the aforementioned. The second monitor light emitting element 166 is formed in the same step with the same conditions so as to have the same configuration as the second light emitting element 14. Therefore, the second monitor light emitting element 166 and the second light emitting element 14 have the same or almost the same characteristics against a change in an environmental temperature and deterioration with time. The second monitor light emitting element 166 is connected to the power source 18. Here, the power source connected to the second light emitting element 14 and the power source connected to the second monitor light emitting element 166 have the same potentials; therefore, they are expressed as the power source 18 with the same reference numeral. It is to be noted in this embodiment mode that the second monitor controlling transistor 115 has p-channel conductivity, however, the invention is not limited to this and the second monitor controlling transistor 115 may have an n-channel conductivity as well. In that case, a circuit configuration in the periphery is appropriately changed.

[0057] A position to provide the monitor circuit 64 is not limited, and it may be provided between the signal line driver circuit 43 and the pixel portion 40 or between the first or the second scan line driver circuit 41 or 42 and the pixel portion 40.

[0058] A buffer amplifier circuit 110 is provided between the monitor circuit 64 and the pixel portion 40. The buffer

amplifier circuit has such features that an input and an output have the same potentials, with high input impedance and high output current capacitance. Therefore, a circuit configuration can be appropriately determined as long as the circuit has such features.

[0059] In such a configuration, the buffer amplifier circuit has a function to change a voltage applied to the first light emitting element 13 and the second light emitting element 14 included in the pixel portion 40 in accordance with a change in potential of one electrode of each of the first monitor light emitting element 66 and the second monitor light emitting element 166.

[0060] In such a configuration, the constant current source 105 and the buffer amplifier circuit 110 in a control circuit 100 may be provided over the same insulating substrate 20 or different substrates.

[0061] In the aforementioned configuration, a constant current is supplied from the constant current source 105 to the first monitor light emitting element 66 and the second monitor light emitting element 166. When an environmental temperature changes or deterioration with time occurs in such a state, the resistance of the first monitor light emitting element 66 and the second monitor light emitting element 166 change. For example, when deterioration with time occurs, the resistance of the first monitor light emitting element 66 and the second monitor light emitting element 166 increase. As a result, potential differences between opposite ends of the first monitor light emitting element 66 and the second monitor light emitting element 166 change since current values supplied to the first monitor light emitting element 66 and the second monitor light emitting element 166 are constant. In specific, potential differences between opposite electrodes of the first monitor light emitting element 66 and the second monitor light emitting element 166 change. At this time, a potential of the electrode connected to the power source 18 is fixed, therefore, a potential of an electrode connected to the constant current source 105 changes. This change in potential of the electrode is supplied to the buffer amplifier circuit 110 through the power supply line 113.

[0062] In other words, a change in potential of the aforementioned electrode is inputted to the input terminal of the buffer amplifier circuit 110. Moreover, a potential outputted from the output terminal of the buffer amplifier circuit 110 is supplied to the first light emitting element 13 and the second light emitting element 14 through the first driving transistor 12 and the second driving transistor 114. In specific, the outputted potential is given as a potential of one electrode of the first light emitting element 13 and the second light emitting element 14.

[0063] In this manner, changes of the first monitor light emitting element 66 and the second monitor light emitting element 166 caused by an environmental temperature change and deterioration with time are fed back to the first light emitting element 13 and the second light emitting element 14. As a result, the first light emitting element 13 and the second light emitting element 14 can emit light at luminance in accordance with the environmental temperature change and deterioration with time. Therefore, a display device which can perform display independent of an environmental temperature change and deterioration with time can be provided.

[0064] Further, as a plurality of the first monitor light emitting elements 66 and the second monitor light emitting elements 166 are provided, these potential changes can be averaged and supplied to the first light emitting element 13 and the second light emitting element 14. That is, in the invention, it is preferable to provide a plurality of the first monitor light emitting elements 66 and the second monitor light emitting elements 166 since potential changes can be averaged. Further, by providing a plurality of the first monitor light emitting elements 66 and the second monitor light emitting elements 166, one monitor light emitting element can be a substitute for a shorted monitor light emitting element.

[0065] It is preferable to provide the first inverter 112 and the second inverter 116 in addition to the first monitor controlling transistor 111 and the second monitor controlling transistor 115 connected to the first monitor light emitting element 66 and the second monitor light emitting element 166 respectively. These inverters are provided in consideration of an operation defect of the monitor circuit 64 caused by a defect (including an initial defect or a defect occurring with time) of the first monitor light emitting element 66 and the second monitor light emitting element 166. For example, in the case where the constant current source 105 and the first monitor controlling transistor 111 and the second monitor controlling transistor 115 are connected without any other transistors or the like, an anode and a cathode of a certain first monitor light emitting element 66 and a certain second monitor light emitting element 166 are shorted (short-circuit) among a plurality of monitor light emitting elements due to a defect in a manufacturing step or the like. Then, a current supplied from the constant current source 105 is supplied more to the shorted first monitor light emitting element 66 and the shorted second monitor light emitting element 166 through the power supply line 113. As the plurality of monitor light emitting elements are connected in parallel, if more current is supplied to the shorted first monitor light emitting element 66 and the shorted second monitor light emitting element 166, a predetermined constant current is not supplied to the other monitor light emitting elements. As a result, an appropriate potential change of the first monitor light emitting element 66 and the second monitor light emitting element 166 cannot be supplied to the first light emitting element 13 and the second light emitting element 14.

[0066] A short-circuit of the monitor light emitting element means that an anode and a cathode of the monitor light emitting element have the same potentials. For example, a short-circuit could occur due to a dust or the like between an anode and a cathode in the manufacturing step. Moreover, in addition to the short-circuit between the anode and the cathode, the monitor light emitting element could be shorted due to a short-circuit between a scan line and an anode, or the like.

[0067] In view of this, in this embodiment mode, the first inverter 112 and the second inverter 116 are provided in addition to the first monitor controlling transistor 111 and the second monitor controlling transistor 115. The first monitor controlling transistor 111 and the second monitor controlling transistor 115 block a current supply to the first monitor light emitting element 66 and the second monitor light emitting element 166 in order to prevent a large amount of current supply due to a short-circuit or the like of the first monitor

light emitting element 66 and the second monitor light emitting element 166 as described above. That is, a shorted monitor light emitting element and a monitor line are electrically cut off.

[0068] The first inverter 112 and the second inverter 116 have a function to output a potential to turn off a monitor controlling transistor when any of the plurality of monitor light emitting elements is shorted. In addition, the first inverter 112 and the second inverter 116 have a function to turn on the monitor controlling transistor when none of the plurality of monitor light emitting elements is shorted.

[0069] A specific operation of the monitor circuit 64 is described with reference to FIGS. 6A and 6B. As shown in FIG. 6A, when an electrode on a high potential side of the first monitor light emitting element 66 is an anode electrode 66a and an electrode on a low potential side is a cathode electrode 66c, the anode electrode 66a is connected to an input terminal of the first inverter 112 and the cathode electrode 66c is connected to the power source 18 and has a fixed potential. Therefore, when an anode and a cathode of the first monitor light emitting element 66 are shorted, a potential of the anode electrode 66a becomes close to that of the cathode electrode 66c. As a result, a low potential close to the potential of the cathode electrode 66c is supplied to the first inverter 112, therefore, a p-channel transistor 112p included in the first inverter 112 is turned on. Then, a potential (Va) on a high potential side is outputted from the first inverter 112 and applied as a gate potential of the first monitor controlling transistor 111. That is, the potential inputted to the gate of the first monitor controlling transistor 111 becomes Va and the first monitor controlling transistor 111 is turned off.

[0070] Similarly, when an electrode on a high potential side of the second monitor light emitting element 166 is an anode electrode 166a and an electrode on a low potential side is a cathode electrode 166c, the anode electrode 166a is connected to an input terminal of the second inverter 116 and the cathode electrode 166c is connected to the power source 18 and has a fixed potential. Therefore, when an anode and a cathode of the second monitor light emitting element 166 are shorted, a potential of the anode electrode 166a becomes close to that of the cathode electrode 166c. As a result, a low potential close to the potential of the cathode electrode 166c is supplied to the second inverter 116, therefore, a p-channel transistor 116p included in the second inverter 116 is turned on. Then, a potential (Va) on a high potential side is outputted from the second inverter 116 and applied as a gate potential of the second monitor controlling transistor 115. That is, the potential inputted to the gate of the second monitor controlling transistor 115 becomes Va and the second monitor controlling transistor 115 is turned off.

[0071] It is to be noted that VDD to be a high potential (High) is set equal to or higher than an anode potential. Moreover, a low potential (Low) of the first inverter 112 and the second inverter 116, a potential of the power source 18, a potential on a low side of the power supply line 113, and a potential on a low side applied to Va can be all set equal. In general, the low side potential is set at ground. However, the invention is not limited to this and the low side potential may be determined so as to have a predetermined potential difference from a high side potential. The predetermined potential difference may be determined depending on a

current, a voltage, luminance characteristics of a light emission material or the specifications of a device.

[0072] Here, an order to supply a constant current to the first monitor light emitting element 66 and the second monitor light emitting element 166 is required to be paid attention to. A constant current is required to start to be supplied to the power supply line 113 when the first monitor controlling transistor 111 and the second monitor controlling transistor 115 are on. In this embodiment mode, as shown in FIG. 6B, a current starts to be supplied to the power supply line 113 with Va remaining Low. After the potential of the power supply line 113 is saturated, Va is set to be VDD. As a result, a capacitor and parasitic capacitance attached to the power supply line 113 can be charged even when the first monitor controlling transistor 111 and the second monitor controlling transistor 115 are on.

[0073] Meanwhile, in the case where the first monitor light emitting element 66 and the second monitor light emitting element 166 are not shorted, potentials of the anode electrode 66a and the anode electrode 166a are supplied to the first inverter 112 and the second inverter 116. Therefore, n-channel transistors 112n and 116n are turned on. As a result, a potential on a low potential side is outputted from the first inverter 112 and the second inverter 116, thereby the first monitor controlling transistor 111 and the second monitor controlling transistor 115 are turned on.

[0074] In this manner, a current supply from the constant current source 105 to a shorted monitor light emitting element can be blocked. Therefore, when a monitor light emitting element is shorted in the case where there are a plurality of monitor light emitting elements, by blocking a current supply to the shorted monitor light emitting element, a potential change of the power supply line 113 can be suppressed to be the least. As a result, an appropriate potential change of the first monitor light emitting element 66 and the second monitor light emitting element 166 can be supplied to the first light emitting element 13 and the second light emitting element 14.

[0075] It is to be noted in this embodiment mode that the constant current source 105 is only required to be a circuit which can supply a constant current. For example, the constant current source 105 can be formed of a transistor. In this embodiment mode, a monitor circuit 64 includes a plurality of monitor light emitting elements, monitor controlling transistors, and inverters; however, the invention is not limited to this. For example, the inverter may be any circuit which has a function to block a current supply to a shorted monitor light emitting element through a monitor line when detecting a short-circuit of the monitor light emitting element. In specific, a function to turn off the monitor controlling transistor for blocking a current supply to the shorted monitor light emitting element is only required.

[0076] Further, in this embodiment mode, a plurality of monitor light emitting elements are used. In this case, even when one of the monitor elements generates an operation defect, other operating monitor elements can monitor characteristics change of light emitting elements due to an environmental temperature change and deterioration with time; thereby the luminance of the light emitting element in the pixel 10 can be corrected.

[0077] In this embodiment mode, the buffer amplifier circuit 110 is provided for preventing a potential change.

Therefore, another circuit capable of preventing a potential change may be used instead of the buffer amplifier circuit 110. That is, in the case of providing a circuit for preventing a potential change between the first monitor light emitting element 66 and the second monitor light emitting element 166, and the first light emitting element 13 and the second light emitting element 14 when applying the potential of one electrode of the first monitor light emitting element 66 and the second monitor light emitting element 166 to the first light emitting element 13 and the second light emitting element 14 respectively, such a circuit is not limited to the buffer amplifier circuit 110 and a circuit with any configuration such as an operational amplifier circuit may be used.

[0078] Here, in this embodiment mode, other circuit configurations are described with reference to FIG. 2. A circuit configuration shown in FIG. 2 has the same arrangement of elements in each of the pixels 10 and the monitor circuit 64 as that in FIG. 1, however, a power source is connected differently from FIG. 1. That is, a power supply line 117 is provided in addition to the power supply line 113 which is used in common in FIG. 1 so that each subpixel can be driven with an independent power source. In this manner, in this embodiment mode, a power supply line may be independently connected for each subpixel. In that case, each power source may independently have the constant current source 105 and the buffer amplifier circuit 110.

[0079] In this manner, providing a power supply line, and the constant current source 105 and the buffer amplifier circuit 110 in a control circuit 200, which are connected to the power supply line in each subpixel is advantageous in that a current value supplied to the monitor element can be set for each subpixel, thereby the precision of correction can be improved. In the case of performing an area grayscale display by using a subpixel as described in this embodiment mode, characteristics of the first light emitting element 13 and the second light emitting element 14 can be set different. For example, when the luminance of a light emitting element of one subpixel becomes twice as high as the other subpixel in the case where the same voltage is applied to the both subpixels, four grayscales with a luminance ratio of 0, 1, 2, and 3 can be displayed without changing a driving voltage or a light emission duty. In this manner, when the characteristics of the light emitting element in each subpixel are different, the characteristics do not always change in the same way by deterioration and temperature. Therefore, the change in characteristics of a combination of elements with different characteristics become quite complicated. In order to perform correction more accurately, it is effective to group elements with similar characteristics. More accurate correction can be achieved when a power supply line, and the constant current source 105 and the buffer amplifier circuit 110 connected thereto are provided in each subpixel and the characteristics of the first monitor light emitting element 66 and the second monitor light emitting element 166 are the same as those of the pixel 10.

[0080] It is to be noted in this embodiment mode that two subpixels are provided, however, the number of subpixels is not limited to this. Any number of subpixels may be provided as long as they are connected in parallel.

## Embodiment Mode 2

[0081] In this embodiment mode, description is made of a circuit configuration and an operation to turn off a monitor

controlling transistor when a monitor light emitting element is shorted, which is different from the aforementioned embodiment mode. It is to be noted that a pixel circuit including a subpixel is described in Embodiment Mode 1, however, in this embodiment mode, description is made of a circuit configuration to turn off a monitor controlling transistor when a monitor light emitting element provided in each subpixel is shorted. Therefore, description is made for each subpixel and description will not be repeated.

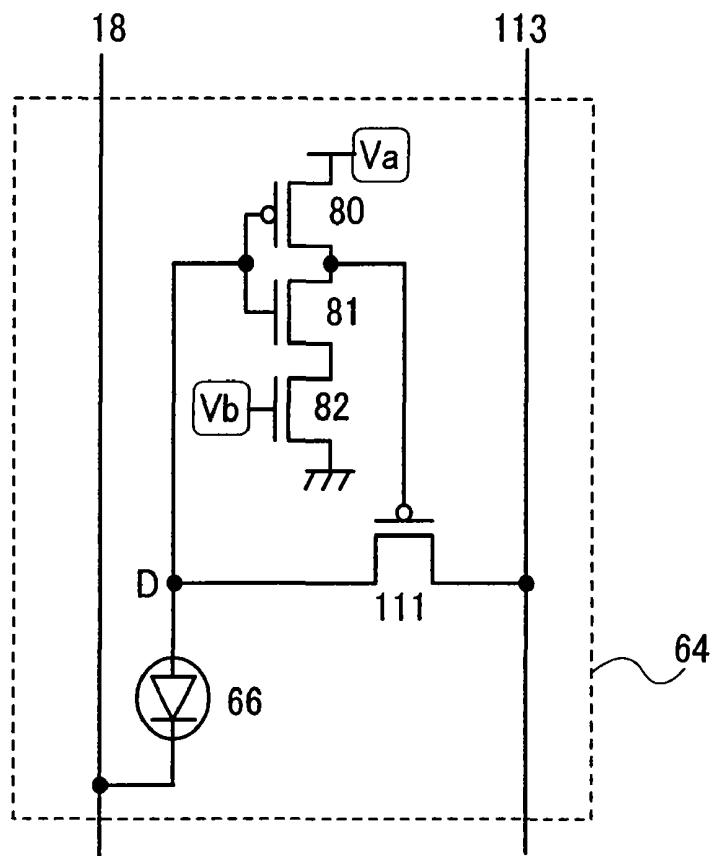

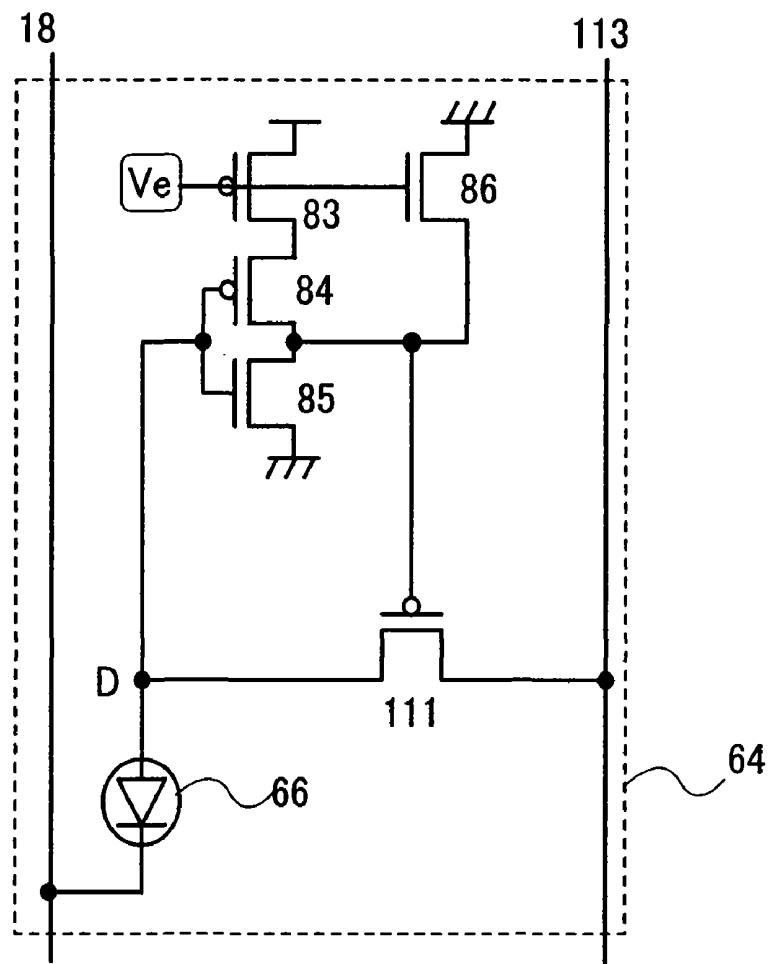

[0082] The monitor circuit **64** shown in FIG. 7A includes a p-channel first transistor **80**, an n-channel second transistor **81** connected in parallel to the first transistor **80** with a common gate electrode, and an n-channel third transistor **82** connected in series to the second transistor **81**. The monitor light emitting element **66** is connected to gate electrodes of first and second transistors **80** and **81**. A gate electrode of a monitor controlling transistor **111** is connected to an electrode to which the first and second transistors **80** and **81** are connected. Other configurations are similar to the monitor circuit **64** shown in FIG. 6A, however, only a subpixel including the monitor controlling transistor **111** and the monitor light emitting element **66** is shown.

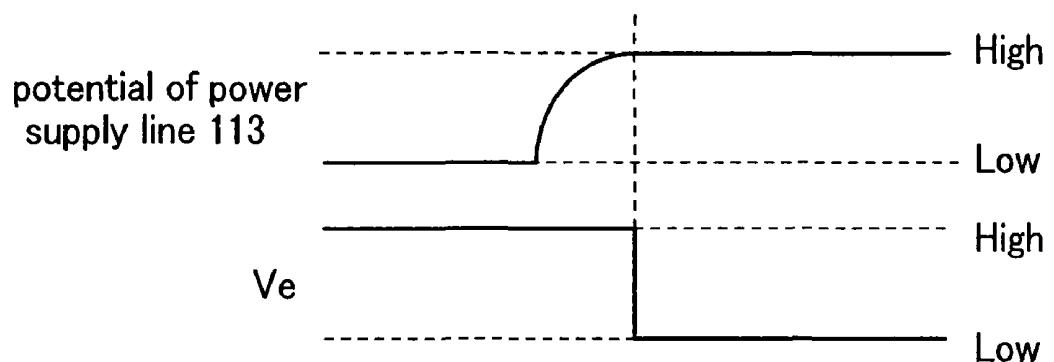

[0083] Further, a potential on a high potential side of the first p-channel transistor **80** is set at  $V_a$  and a potential of a gate electrode of the n-channel third transistor **82** is set at  $V_b$ . Then, the potential of the power supply line **113** and the potentials of  $V_a$  and  $V_b$  are operated as shown in FIG. 7B.

[0084] First, the capacitor and the parasitic capacitance attached to the power supply line **113** are completely charged. After that, the potential of  $V_a$  is set High. In the case where the monitor light emitting element **66** is shorted, a potential of an anode of the monitor light emitting element **66**, that is a potential of a node D is decreased almost as low as that of a cathode of the monitor light emitting element **66**. Then, a low potential, which is Low is inputted to the gate electrodes of the first and second transistors **80** and **81**, thereby the n-channel second transistor **81** is turned off and the p-channel first transistor **80** is turned on. Then, a high side potential of a potential of the first transistor **80** is inputted to the gate electrode of the monitor controlling transistor **111**, thereby the monitor controlling transistor **111** is turned off. As a result, a current from the power supply line **113** is not supplied to the shorted monitor light emitting element **66**.

[0085] At this time, when a shorted state is slight and the potential of the anode is slightly decreased, it is sometimes hard to control either the first or second transistor **80** or **81** to be turned on or off. Therefore, the potential of  $V_b$  is supplied to a gate electrode of the third transistor **82** as shown in FIG. 7B. In other words, the potential of  $V_b$  is set Low while  $V_a$  is High as shown in FIG. 7B. Then, the n-channel third transistor **82** is turned off. As a result, when the potential of the anode is a potential lower than  $VDD$  by a threshold voltage of the first transistor, the first transistor **80** can be turned on and the monitor controlling transistor **111** can be turned off.

[0086] By controlling the potential of  $V_b$  in this manner, the monitor controlling transistor **111** can be accurately turned off even in the case where the potential of the anode is slightly decreased. It is to be noted that when the monitor light emitting element operates normally,  $V_b$  is controlled so that the monitor controlling transistor **111** is turned on. That

is, the potential of the anode becomes almost the same as the high potential of the power supply line **113**; therefore, the second transistor **81** is turned on. As a result, a low potential is applied to the gate electrode of the monitor controlling transistor **111**, and it is turned on.

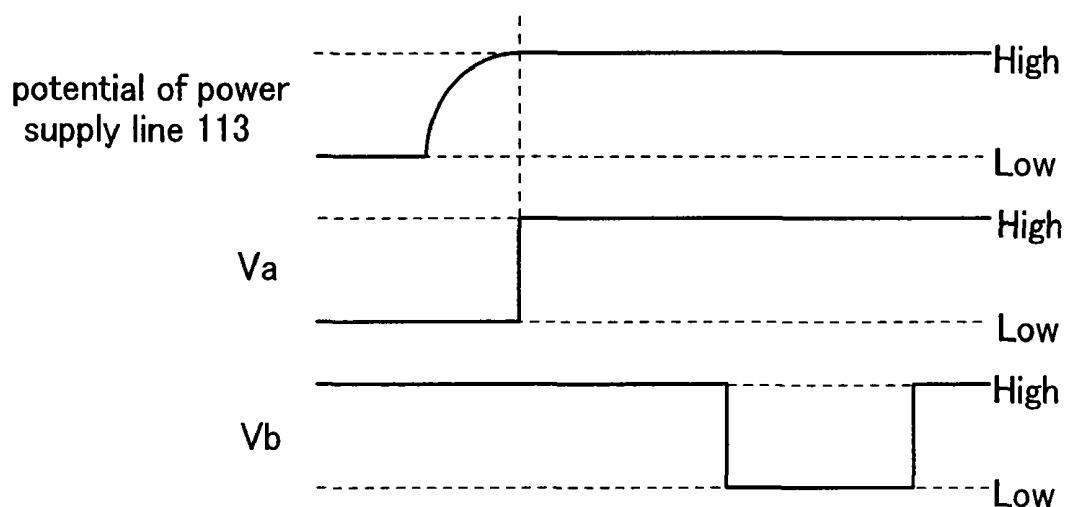

[0087] As shown in FIG. 8A, a p-channel first transistor **83**, a p-channel second transistor **84** connected in series to the first transistor **83**, an n-channel third transistor **85** having a gate electrode in common with the second transistor **84**, and an n-channel fourth transistor **86** connected in parallel to the first transistor **83** with a gate electrode in common are provided. The monitor light emitting element **66** is connected to gate electrodes of the second and third transistors **84** and **85**. The gate electrode of the monitor controlling transistor **111** is connected to an electrode to which the second and third transistors **84** and **85** are connected. Further, the gate electrode of the monitor controlling transistor **111** is connected to one electrode of the fourth transistor **86**. Other configurations are similar to the monitor circuit **64** shown in FIG. 6A.

[0088] First, the capacitor and the parasitic capacitance attached to the power supply line **113** are completely charged. After that, a potential of  $V_e$  is set Low. In the case where the monitor light emitting element **66** is shorted, a potential of the anode of the monitor light emitting element **66**, that is a potential of a node D is decreased almost as low as that of the cathode of the monitor light emitting element **66**. Then, a low potential, which is Low is inputted to the gate electrodes of the second and third transistors **84** and **85**, thereby the n-channel third transistor **85** is turned off and the p-channel second transistor **84** is turned on. When the potential of  $V_e$  is set Low, the first transistor **83** is turned on and the fourth transistor **86** is turned off. Then, a high side potential of a potential of the first transistor is inputted to the gate electrode of the monitor controlling transistor **111** through the second transistor **84**, thereby the monitor controlling transistor **111** is turned off. As a result, a current from the power supply line **113** is not supplied to the shorted monitor light emitting element **66**. By controlling the voltage  $V_e$  of the gate electrode in this manner, the monitor controlling transistor **111** can be accurately turned off.

### Embodiment Mode 3

[0089] A reverse bias voltage can be applied to a light emitting element and a monitor light emitting element. In this embodiment mode, description is made of the case of applying a reverse bias voltage.

[0090] When a voltage applied so that the light emitting element **13** and the monitor light emitting element **66** emit light is called a forward voltage, a reverse bias voltage is a voltage obtained by inverting a high side potential and a low side potential of the forward voltage. In specific, in the monitor light emitting element **66**, the potential of the power supply line **113** is set lower than the potential of the power source **18** so as to invert the potentials of the anode electrode **66a** and the cathode electrode **66c**.

[0091] In specific, as shown in FIG. 14, the potential of the anode electrode **66a** (anode potential:  $V_a$ ) and the potential of the cathode electrode **66c** (cathode potential:  $V_c$ ) are set at Low potentials. At this time, the potential of the power supply line **113** ( $V_{113}$ ) is inverted at the same time. A period in which the anode potential and the cathode potential are

inverted is called a reverse bias voltage applying period. Then, the cathode potential is brought back after a predetermined reverse bias voltage applying period passes and a certain current is supplied through the power supply line 113, thereby charging is completed. That is, after the voltage is saturated, the potential is brought back. At this time, the potential of the power supply line 113 is brought back in a curved shape because a constant current is used for charging a plurality of the monitor light emitting elements and further the parasitic capacitance.

[0092] It is preferable to invert an anode potential prior to inverting a cathode potential. Then, after a predetermined reverse bias voltage applying period passes, the anode potential is brought back and then the cathode potential is brought back. At the same time as when the anode potential is inverted, the potential of the power supply line 113 is charged to be High.

[0093] In this reverse bias voltage applying period, the driving transistor 12 and the monitor controlling transistor 111 are required to be turned on.

[0094] As a result of applying a reverse bias voltage to the light emitting element, defective states of the light emitting element 13 and the monitor light emitting element 66 can be improved, which leads to improved reliability. Moreover, an initial defect may occur in the light emitting element 13 and the monitor light emitting element 66 in that an anode and a cathode are shorted due to a foreign substance, a pinhole caused by a minute projection of the anode or the cathode or unevenness of a light emitting layer. Such an initial defect prevents light emission and non-light emission in accordance with signals, and most of the current flows to the shorted element. As a result, display of an image cannot be performed favorably. Moreover, this defect may occur in an arbitrary pixel.

[0095] When a reverse bias voltage is applied to the light emitting element 13 and the monitor light emitting element 66 as in this embodiment mode, a current flows locally to a shorted portion, thereby the shorted portion generates heat and can be oxidized or carbonized. Consequently, the shorted portion can be insulated. A current flows to other regions than the insulated portion, and the light emitting element 13 and the monitor light emitting element 66 can operate normally. By applying a reverse bias voltage in this manner, an initial defect can be fixed if generated. It is to be noted that such a short-circuit portion is preferably insulated before shipment.

[0096] Moreover, not only an initial defect, but an anode and a cathode may be newly shorted as time passes. Such a defect is also called a progressive defect. In view of this, as in this invention, a reverse bias voltage is applied to the light emitting element 13 and the monitor light emitting element 66 regularly. As a result, a progressive defect can be fixed if generated. Thus, the light emitting element 13 and the monitor light emitting element 66 can operate normally.

[0097] In addition, by applying a reverse bias voltage, image sticking can be prevented. Image sticking is caused by the deterioration of the light emitting element 13. The deterioration can be lowered by applying a reverse bias voltage. As a result, image sticking can be prevented.

[0098] In general, the deterioration of the light emitting element 13 and the monitor light emitting element 66

progresses at a faster rate in the initial period, and the progress rate thereof decreases with time. That is, in the light emitting element 13 and the monitor light emitting element 66 which have already deteriorated in a pixel, further deterioration hardly occurs. As a result, variations are generated in each light emitting element 13. In view of this, all the light emitting elements 13 and the monitor light emitting elements 66 may emit light before shipment, when displaying no image, or the like. By generating deterioration in a pixel which has not deteriorated in this manner, the deterioration levels of all the pixels can be averaged. As described above, a structure of lighting all pixels may be provided in a display device.

#### Embodiment Mode 4

[0099] In this embodiment mode, examples of a pixel circuit and configuration are described. FIG. 3 shows a pixel circuit which can be applied to a pixel portion of the invention. In the pixel portion 40, a data line Sx, a gate line Gy, and a power supply line Vx are provided in matrix, in which pixels 10 are provided at intersections thereof. The pixel 10 includes a switching transistor 11, a driving transistor 12, a capacitor 16, and a light emitting element 13.

[0100] Connections in the pixel are described. The switching transistor 11 is provided at an intersection of the data line Sx and the gate line Gy. One electrode of the switching transistor 11 is connected to the signal line Sx and a gate electrode of the switching transistor 11 is connected to the gate line Gy. One electrode of the driving transistor 12 is connected to the power supply line Vx and a gate electrode thereof is connected to the other electrode of the switching transistor 11. A capacitor 16 is provided so as to hold a gate-source voltage of the driving transistor 12. In this embodiment mode, the capacitor 16 has one electrode connected to Vx and the other electrode connected to the gate electrode of the driving transistor 12. It is to be noted that the capacitor 16 is not required to be provided in the case where the gate capacitance of the driving transistor 12 is large and there is few leak current. The light emitting element 13 is connected to the other electrode of the driving transistor 12.

[0101] A driving method of such a pixel is described. First, when the switching transistor 11 is turned on, a video signal is inputted from the signal line Sx. A charge is accumulated in the capacitor 16 based on the video signal. When the charge accumulated in the capacitor 16 becomes higher than a gate-source voltage (Vgs) of the driving transistor 12, the driving transistor 12 is turned on. Then, a current is supplied to the light emitting element 13 and it emits light. At this time, the driving transistor 12 can operate in a linear region or a saturation region. In the saturation region, the driving transistor 12 can supply a constant current. In the linear region, the driving transistor 12 can operate at a low voltage; thereby low power consumption can be achieved.

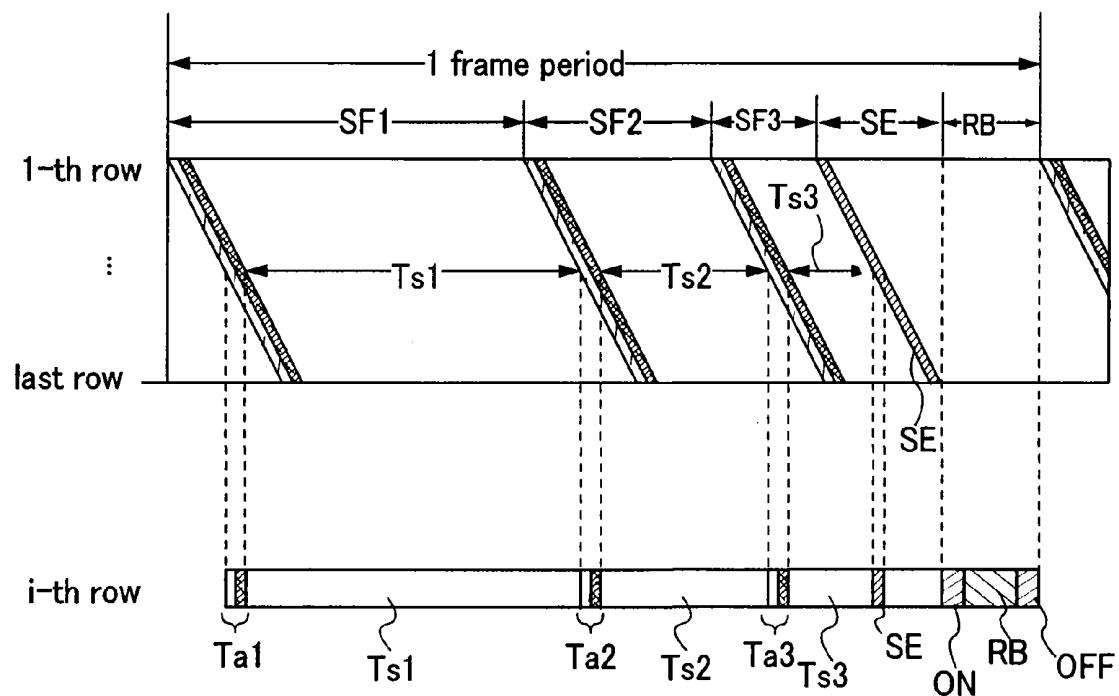

[0102] Hereinafter, a driving method of a pixel is described with reference to a timing chart. FIG. 9A is a timing chart of one frame period in the case where an image is rewritten 60 frames a second. A longitudinal axis indicates a scan line (first to last rows) and a horizontal axis indicates time in the timing chart.

[0103] One frame period includes m (m is a natural number of 2 or larger) subframe periods SF1, SF2, . . . , and SFm. The m subframe periods SF1, SF2, . . . , and SFm each

has writing operation periods Ta1, Ta2, . . . , and Tam, display periods (light emission periods) Ts1, Ts2, . . . , and Tsm, and a reverse bias voltage applying period. In this embodiment mode, as shown in FIG. 9A, one frame period includes subframe periods SF1, SF2, and SF3 and a reverse bias voltage applying period (RB). In each subframe period, the writing operation periods Ta1 to Ta3 are sequentially performed, which are followed by the display periods Ts1 to Ts3 respectively.

[0104] A timing chart shown in FIG. 9B includes a writing operation period, a display period, and a reverse bias voltage applying period of a certain row (i-th row). After the writing operation period and the display period are alternately performed, the reverse bias voltage applying period starts. The period including the writing operation period and the display period becomes a forward voltage applying period.

[0105] The writing operation period Ta can be divided into a plurality of operation periods. In this embodiment mode, the writing operation period Ta is divided into two operation periods, in which an erasing operation is performed in one period and a writing operation is performed in the other period. In this manner, a WE (Write Erase) signal is inputted in order to provide an erasing operation and a writing operation. Other erasing operations and writing operations, and signals are specifically described in the following embodiment mode. Moreover, right before the reverse bias voltage applying period, a period to simultaneously turn on the switching transistors in all pixels, that is a period (On period) to turn on all scan lines is provided.

[0106] It is preferable to provide a period to simultaneously turn off the switching transistors in all pixels, that is a period (Off period) to turn off all scan lines immediately after the reverse bias voltage applying period. Moreover, an erasing period (SE) is provided right before the reverse bias voltage applying period. The erasing period can be performed by a similar operation to the aforementioned erasing operation. In the erasing period, operations to sequentially erase the data written in the preceding subframe period, which is SF3 in this embodiment mode are sequentially performed. In the on-period, the switching transistors are turned on all at once after the display period of the pixel in the last row is terminated. Therefore, a pixel of the first row has an unnecessary display period.

[0107] The control for providing such an On period, an Off period, and an erasing period is carried out by driver circuits such as a scan line driver circuit and a signal line driver circuit. Note that the timing to apply a reverse bias voltage to the light emitting element 13, namely the reverse bias voltage applying period is not limited to those shown in FIGS. 9A and 9B. That is to say, the reverse bias voltage applying period is not necessarily provided for each frame period, nor in the latter part of one frame period. The On period is only required to be provided immediately before the applying period (RB) and the Off period is only required to be provided immediately after the applying period (RB). In addition, the order of inverting the voltages of the anode and the cathode of the light emitting element is not limited to those shown in FIGS. 9A and 9B. That is, the potential of the anode electrode may be decreased after the potential of the cathode electrode is increased.

[0108] FIG. 4 shows a layout example of the pixel circuit shown in FIG. 3. A semiconductor film is formed to con-

stitute the switching transistor 11 and the driving transistor 12. Then, a first conductive film is formed with an insulating film functioning as a gate insulating film interposed therebetween. The conductive film is used as gate electrodes of the switching transistor 11 and the driving transistor 12, and can also be used as a gate line Gy. At this time, the switching transistor 11 preferably has a double gate structure.

[0109] Subsequently, a second conductive film is formed with an insulating film functioning as an interlayer insulating film interposed therebetween. The conductive film is used as drain and source wires of the switching transistor 11 and the driving transistor 12, and can also be used as the signal line Sx and the power supply line Vx. At this time, the capacitor 16 can be formed by stacking the first conductive film, the insulating film functioning as an interlayer insulating film, and the second conductive film. The gate electrode of the driving transistor 12 is connected to the other electrode of the switching transistor through a contact hole.

[0110] A first electrode 19 (pixel electrode) is formed in an opening provided in the pixel. The pixel electrode is connected to the other electrode of the driving transistor 12. If an insulating film or the like is formed between the second conductive film and the pixel electrode at this time, the pixel electrode is required to be connected to the other electrode of the driving transistor 12 through a contact hole. If an insulating film or the like is not formed, the pixel electrode can be connected directly to the other electrode of the driving transistor 12.

[0111] In the layout as shown in FIG. 4, the first conductive film and the pixel electrode may overlap in order to achieve a high aperture ratio. In such an area, coupling capacitance may occur. Such coupling capacitance is unwanted capacitance.

[0112] FIG. 5 is a cross sectional view taken along A-B and B-C in FIG. 4. A semiconductor film is formed over the insulating substrate 20 with a base film interposed therebetween. As the insulating substrate 20, a glass substrate formed of barium borosilicate glass or alumino borosilicate glass, a quartz substrate, a stainless steel substrate or the like may be used. Alternatively, a synthetic resin substrate having flexibility such as a plastic substrate typified by PET (Polyethylene Terephthalate), or PEN (Polyethylene Naphthalate) and an acrylic substrate can be used as long as it can withstand the processing temperatures during the manufacturing steps although it generally has a lower heat resistance temperature as compared to other substrates. As a base film, an insulating film formed of silicon oxide, silicon nitride, silicon nitride oxide, or the like can be used.

[0113] An amorphous semiconductor film is formed over the base film so as to have a thickness of 25 to 100 nm (preferably, 30 to 60 nm). Silicon germanium as well as silicon can be used for the amorphous semiconductor.

[0114] The amorphous semiconductor film is crystallized as required to form a crystalline semiconductor film. The crystallization can be performed by using an annealing furnace, laser irradiation, irradiation of light emitted from a lamp (hereinafter referred to as lamp annealing), or a combination of them. For example, a crystalline semiconductor film is formed by adding a metal element to an amorphous semiconductor film and applying heat treatment using an annealing furnace. A semiconductor film is preferably added

with a metal element since it can be crystallized at a low temperature. Thus formed crystalline semiconductor film is processed into a predetermined shape. The predetermined shape is to be the switching transistor **11** and the driving transistor **12** as shown in FIG. 4.

[0115] Then, an insulating film functioning as a gate insulating film is formed. The insulating film is formed so as to have a thickness of 10 to 150 nm, and preferably 20 to 40 nm, and cover the semiconductor film. The insulating film may have a single layer structure or a stacked-layer structure using a silicon oxynitride film, a silicon oxide film or the like.

[0116] A first conductive film functioning as a gate electrode is formed over the semiconductor film with a gate insulating film interposed therebetween. The gate electrode may have a single layer structure or a stacked-layer structure, though a stacked-layer structure of conductive films **22a** and **22b** is used in this embodiment mode. Each of the conductive films **22a** and **22b** may be formed by using an element selected from Ta, Ti, W, Mo, Al, and Cu, or an alloy or a compound material mainly containing such an element. In this embodiment mode, the conductive film **22a** is formed of a tantalum nitride film with a thickness of 10 to 50 nm, for example 30 nm, and the conductive film **22b** is stacked thereover using a tungsten film with a thickness of 200 to 400 nm, for example 370 nm.

[0117] An impurity element is added with the gate electrode used as a mask. At this time, a low concentration impurity region may be formed in addition to a high concentration impurity region, which is called an LDD (Lightly Doped Drain) structure. In specific, a structure where the low concentration impurity region overlaps the gate electrode is called a GOLD (Gate-drain Overlapped LDD) structure. An N-channel transistor preferably has the low concentration impurity region in particular.

[0118] Subsequently, insulating films **28** and **29** functioning as an interlayer insulating film **30** are formed. The insulating film **28** may be formed of an insulating film containing nitrogen, and in this embodiment mode, a silicon nitride film with a thickness of 100 nm is formed by a plasma CVD method.

[0119] Meanwhile, the insulating film **29** may be formed by using an organic material or an inorganic material. The organic material includes polyimide, acrylic, polyamide, polyimide amide, resist, benzocyclobutene, siloxane, and polysilazane. Siloxane has a skeleton structure formed by the bond of silicon (Si) and oxygen (O), in which a polymer material containing at least hydrogen as a substituent or at least one of fluorine, an alkyl group, or aromatic hydrocarbon as the substituent is used as a starting material. Polysilazane is a polymer material having the bond of silicon (Si) and nitrogen (N), namely polysilazane. The inorganic material includes an insulating film containing oxygen or nitrogen such as silicon oxide ( $\text{SiO}_x$ ), silicon nitride ( $\text{SiN}_x$ ), silicon oxynitride ( $\text{SiO}_x\text{N}_y$ ) ( $x>y$ ), and silicon nitride oxide ( $\text{SiN}_x\text{O}_y$ ) ( $x>y$ ) ( $x, y=1, 2 \dots$ ). Further, the insulating film **29** may have a stacked layer structure of these insulating films. In specific, when the insulating film **29** is formed by using an organic material, uniformity is improved whereas moisture and oxygen are absorbed by the organic material. In order to prevent this, an insulating film containing an inorganic material may be formed over the organic material.

An insulating film containing nitrogen is preferably used as the inorganic material since alkali ions such as Na can be prevented from entering. An organic material is preferably used for the insulating film **29** since uniformity can be improved.

[0120] A contact hole is formed in the interlayer insulating film **30**. Then, a second conductive film is formed, which functions as source and drain wirings **24** of the switching transistor **11** and the driving transistor **12**, the signal line Sx, and the power supply line Vx. The second conductive film may be formed by using an element such as aluminum (Al), titanium (Ti), molybdenum (Mo), tungsten (W), and silicon (Si), or an alloy film using such elements. In this embodiment mode, the second conductive film is formed by stacking a titanium (Ti) film, a titanium nitride (TiN) film, a titanium-aluminum alloy film, and a titanium film, which have thicknesses of 60 nm, 40 nm, 300 nm, and 100 nm respectively. Then, an insulating film **31** is formed so as to cover the second conductive film. The insulating film **31** can be formed by using any of the materials of the interlayer insulating film **30** described above. A high aperture ratio can be achieved by providing such insulating film **31**.

[0121] A first electrode (a pixel electrode) **19** is formed in the opening provided in the insulating film **31**. In order to increase the step coverage of the pixel electrode in the opening, the end portion of the opening is preferably roundish so as to have a plurality of radii of curvature. The first electrode **19** may be formed by using a light transmissive material such as indium tin oxide (ITO), indium zinc oxide (IZO) obtained by mixing 2 to 20% of zinc oxide (ZnO) into indium oxide, ITO— $\text{SiO}_x$  obtained by mixing 2 to 20% of silicon oxide ( $\text{SiO}_2$ ) into indium oxide, organic indium, and organotin. The pixel electrode **19** may also be formed by using a light shielding material such as an element selected from silver (Ag), tantalum, tungsten, titanium, molybdenum, aluminum, and copper, or an alloy or compound material mainly containing such an element. When the insulating film **31** is formed by using an organic material to improve uniformity, the surface uniformity on which the pixel electrode is formed is improved, which allows a constant voltage to be applied and prevents a short-circuit.

[0122] Unwanted coupling capacitance may occur in the area **430** where the first conductive film overlaps the pixel electrode **19**. This is unwanted coupling capacitance.

[0123] Subsequently, a partition wall **32** is formed and a light emitting layer **33** is formed by a vapor deposition method or an ink jet printing method. The light emitting layer **33** is formed by arbitrarily combining an electron injection layer (EIL), an electron transporting layer (ETL), a light emitting layer (EML), a hole transporting layer (HTL), a hole injection layer (HIL) and the like using an organic material or an inorganic material. Note that the boundaries between each layer are not necessarily clearly defined, and there is also a case where materials of the respective layers are partially mixed with each other, which blurs the boundaries. The structure of the light emitting layer **33** is not limited to the aforementioned stacked-layer structure.

[0124] As a host material for forming the light emitting layer **33**, an inorganic material can be used. As an inorganic material, it is preferable to use sulfide, oxide, or nitride of a metal material such as zinc, cadmium, and gallium. For

example, as sulfide, zinc sulphide ( $ZnS$ ), cadmium sulfide ( $CdS$ ), calcium sulfide ( $CaS$ ), yttrium sulfide ( $Y_2S_3$ ), gallium sulfide ( $Ga_2S_3$ ), strontium sulfide ( $SrS$ ), or barium monosulfide ( $BaS$ ) or the like can be used. As oxide, zinc oxide ( $ZnO$ ), yttrium oxide ( $Y_2O_3$ ), or the like can be used. In addition, as nitride, aluminum nitride ( $AlN$ ), gallium nitride ( $GaN$ ), indium nitride ( $InN$ ), or the like can be used. Furthermore, zinc selenide ( $ZnSe$ ), zinc telluride ( $ZnTe$ ), or the like can be used as well. Alternatively, ternary mixed crystal such as calcium sulfide-gallium ( $CaGa_2S_4$ ), strontium sulfide-gallium ( $SrGa_2S_4$ ), or barium sulfide-gallium ( $BaGa_2S_4$ ), may be used.

[0125] As an impurity element, a metal element such as manganese ( $Mn$ ), copper ( $Cu$ ), samarium ( $Sm$ ), terbium ( $Th$ ), erbium ( $Er$ ), thulium ( $Tm$ ), europium ( $Eu$ ), cerium ( $Ce$ ), or praseodymium ( $Pr$ ) can be used to form a light emission center using inner-shell electron transition of a metal ion. As charge compensation, a halogen element such as fluorine ( $F$ ) or chlorine ( $Cl$ ) may be added.

[0126] In addition, as a light emission center using donor-acceptor recombination, a light emitting material including the first impurity element and the second impurity element can be used. For example, as the first impurity element, metal elements such as copper ( $Cu$ ), silver ( $Ag$ ), gold ( $Au$ ), and platinum ( $Pt$ ), or silicon ( $Si$ ) can be used. The second impurity element can be, for example, fluorine ( $F$ ), chlorine ( $Cl$ ), bromine ( $Br$ ), iodine ( $I$ ), boron ( $B$ ), aluminum ( $Al$ ), gallium ( $Ga$ ), indium ( $In$ ), thallium ( $Tl$ ), or the like.

[0127] A light-emitting material is obtained by solid phase reaction, namely weighing a host material and an impurity element, mixing them in a mortar, and heating it in an electric furnace so that an impurity element is contained in the host material. For example, the host material and a first impurity element or a compound including the first impurity element, a second impurity element or a compound including the second impurity element are weighed. After mixing them in a mortar, it is heated and baked in an electric furnace. A baking temperature is preferably 700 to 1500° C. When the temperature is too low, the solid phase reaction does not advance while the host material is decomposed when the temperature is too high. Note that the composition may be baked in a powder state, however, it is preferable to perform baking in a pellet state.

[0128] Further, as an impurity element in the case of utilizing solid phase reaction, a compound formed of the first impurity element and the second impurity element may be used in combination. In this case, the solid phase reaction easily advances since the impurity elements are easily dispersed. Therefore, an even light emitting material can be obtained. Moreover, as no unnecessary impurity elements are mixed, a light emitting material with high purity can be obtained. As a compound formed of the first impurity element and the second impurity element, for example, copper fluoride ( $CuF_2$ ), copper chloride ( $CuCl$ ), copper iodide ( $CuI$ ), copper bromide ( $CuBr$ ), copper nitride ( $Cu_3N$ ), copper phosphide ( $Cu_3P$ ), silver fluoride ( $CuF$ ), silver chloride ( $CuCl$ ), silver iodide ( $CuI$ ), a silver bromide ( $CuBr$ ), gold chloride ( $AuCl_3$ ), gold bromide ( $AuBr_3$ ), platinum chloride ( $PtCl_2$ ), or the like can be used. In addition, a light emitting material including the third impurity element instead of the second impurity element may be used.

[0129] For example, the third impurity element can be lithium ( $Li$ ), sodium ( $Na$ ), potassium ( $K$ ), rubidium ( $Rb$ ),

cesium ( $Cs$ ), nitrogen ( $N$ ), phosphorus ( $P$ ), arsenic ( $As$ ), antimony ( $Sb$ ), bismuth ( $Bi$ ), or the like. These impurity elements are preferably contained at a concentration of 0.01 to 10 mol %, and preferably in a range of 0.1 to 5 mol % in the host material.

[0130] As a light emitting material having high electric conductivity, the material described above is used as a host material, thereby a light emitting material to which a light emitting material including the first impurity element, the second impurity element and the third impurity element can be used. These impurity elements are preferably contained at a concentration of 0.01 to 10 mol %, and preferably in a range of 0.1 to 5 mol % in the host material.

[0131] As a compound formed of the second impurity element and the third impurity element, for example, alkali halide such as lithium fluoride ( $LiF$ ), lithium chloride ( $LiCl$ ), lithium iodide ( $LiI$ ), copper bromide ( $LiBr$ ), and sodium chloride ( $NaCl$ ), boron nitride ( $BN$ ), aluminum nitride ( $AlN$ ), aluminum antimony ( $AlSb$ ), gallium phosphorus ( $GaP$ ), gallium arsenide ( $GaAs$ ), indium phosphorus ( $InP$ ), indium arsenic ( $InAs$ ), indium antimonide ( $InSb$ ), or the like can be used.

[0132] By using the aforementioned material as a host material, a light emitting layer formed by using a light emitting material including the aforementioned first impurity element, second impurity element, and third impurity element can emit light without a hot electron accelerated by a high electric field. That is to say, it is not necessary to apply high voltage to a light emitting element, therefore, the light emitting element which can operate with a low driving voltage can be obtained. Moreover, because the light emitting element can emit light with a low driving voltage, power consumption can be reduced. Moreover, the element which becomes another light emission center may further be included.

[0133] Moreover, by using the material as a host material, a light emitting material including a light emission center using inner-shell electron transition of the second impurity element and the third impurity element and the aforementioned metal ion can be used. In this case, it is desirable that a metal ion becoming a light emission center be contained at a concentration of 0.05 to 5 atom % in the host material. Moreover, it is preferable that the concentration of the second impurity element be 0.05 to 5 atom % in the host material. Moreover, it is preferable that the concentration of the third impurity element be 0.05 to 5 atom % in the host material. A light emitting material with such a structure can emit light with a low voltage. Therefore, a light emitting element which can emit light with a low driving voltage with reduced power consumption can be obtained. Moreover, the element which become another light emission center may further be included. Luminance decay of a light emitting element can be suppressed by using such a light emitting material. Moreover, a light emitting element can be driven with a low voltage by using a transistor.

[0134] A second electrode **35** is formed by a vapor deposition method. The first electrode (pixel electrode) **19** and the second electrode **35** of the light emitting element function as an anode or a cathode depending on a pixel configuration. The anode is preferably formed using a metal, an alloy, a conductive compound, and a mixture thereof, each of which has a high work function (work function of 4.0 eV

or higher). More specifically, it is possible to use ITO, IZO obtained by mixing 2 to 20% of zinc oxide (ZnO) into indium oxide, gold (Au), platinum (Pt), nickel (Ni), tungsten (W), chromium (Cr), molybdenum (Mo), iron (Fe), cobalt (Co), copper (Cu), palladium (Pd), nitride of a metal material (TiN), or the like.

[0135] The cathode is preferably formed using a metal, an alloy, a conductive compound, and a mixture thereof, each of which has a low work function (work function of 3.8 eV or lower). More specifically, it is possible to use an element belonging to group 1 or group 2 of the periodic table, namely an alkali metal such as Li and Cs, an alkaline earth metal such as Mg, Ca and Sr, an alloy (Mg:Ag, Al:Li) or a compound (LiF, CsF, CaF<sub>2</sub>) containing them, and a transition metal including a rare earth metal. Since the cathode is required to transmit light, these metals or alloys containing them are formed extremely thin and stacked with a metal (including an alloy) such as ITO.

[0136] A protective film may be formed thereafter so as to cover the second electrode 35. As the protective film, a silicon nitride film or a DLC film may be used. In this manner, the pixel of the display device can be formed.

#### Embodiment Mode 5

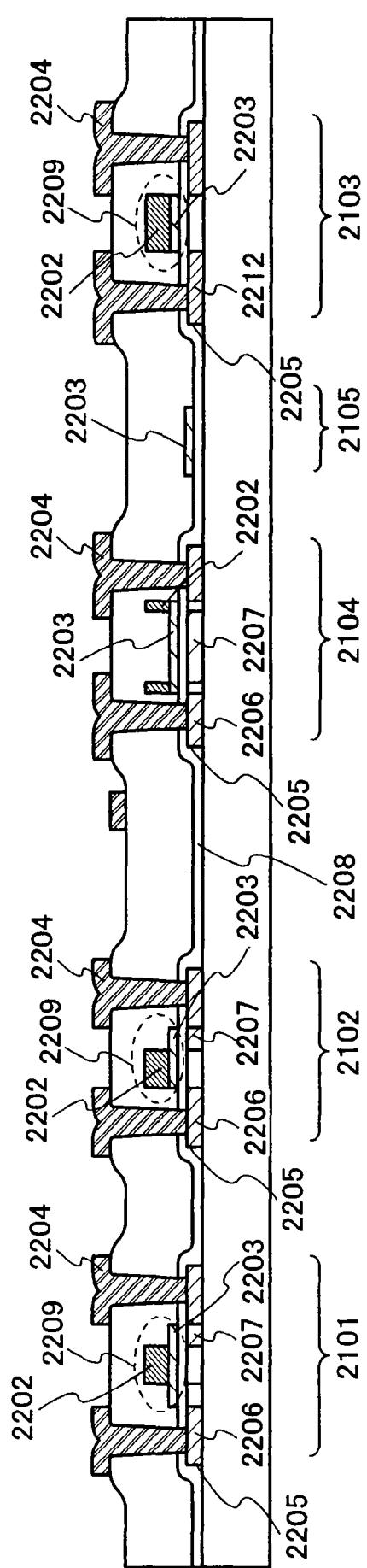

[0137] Configurations of a pixel and a driver circuit of a display device of the invention are described with reference to FIGS. 29 to 31.

[0138] FIG. 29 shows a configuration of a display panel of the invention. This display panel includes a pixel portion 121 in which subpixels 130 are arranged in a plurality of columns, a scan line driver circuit 122 which controls a signal of a scan line 133, and a data line driver circuit 123 which controls a signal of a data line 131 over a substrate 120. Moreover, a monitor circuit 124 for correcting a luminance change of a light emitting element 137 included in the subpixel 130 may be provided as well. The light emitting element 137 and a light emitting element included in the monitor circuit 124 have the same structures. The light emitting element 137 has a structure in which a layer containing a material which exhibits electroluminescence is sandwiched between a pair of electrodes.

[0139] Input terminals 125 for inputting signals from an external circuit to the scan line driver circuit 122, input terminals 126 for inputting signals from an external circuit to the data line driver circuit 123, and an input terminal 129 for inputting signals to the monitor circuit 124 are provided in the periphery of the substrate 120.

[0140] The subpixel 130 includes a transistor 134 connected to the data line 131 and a transistor 135 which is connected between the power supply line 132 and the light emitting element 137 in series. A gate of the transistor 134 is connected to the scan line 133. When the transistor 134 is selected by a scan signal, it inputs a signal of the data line 131 to the subpixel 130. The inputted signal is applied to a gate of the transistor 135 and charges a holding capacitor portion 136. In accordance with this signal, the power supply line 132 and the light emitting element 137 become conductive, thereby the light emitting element 137 emits light.

[0141] A power is required to be supplied from an external circuit so that the light emitting element 137 provided in the

subpixel 130 emits light. The power supply line 132 provided in the pixel portion 121 is connected to the external circuit at input terminals 127. As resistance loss occurs in the power supply line 132 depending on the length of a wire to be led, it is preferable to provide the input terminals 127 at a plurality of positions in the periphery of the substrate 120. The input terminals 127 are provided at opposite end portions of the substrate 120 so that luminance variations in the area of the pixel portion 121 do not become notable. That is, it is prevented that one side of the screen becomes bright while the other side thereof becomes dark. Further, in the light emitting element 137 having a pair of electrodes, an electrode on the opposite side to the electrode connected to the power supply line 132 is formed as a common electrode shared by the plurality of subpixels 130. In order to reduce the resistance loss of this electrode, a plurality of terminals 128 are provided.

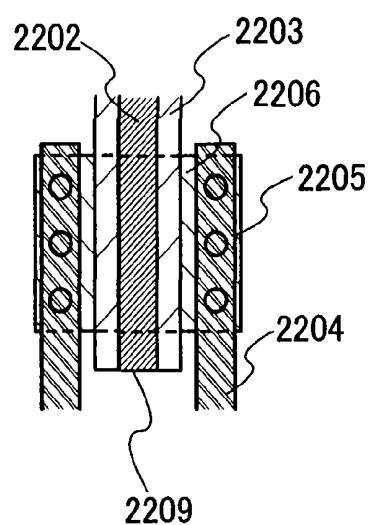

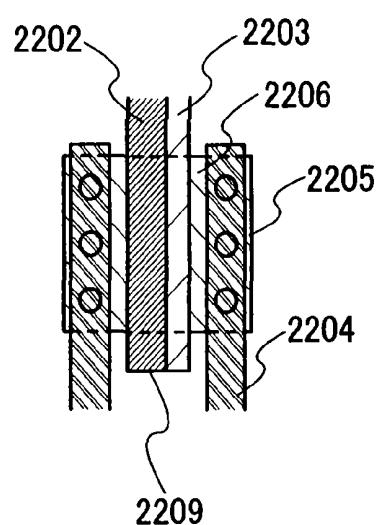

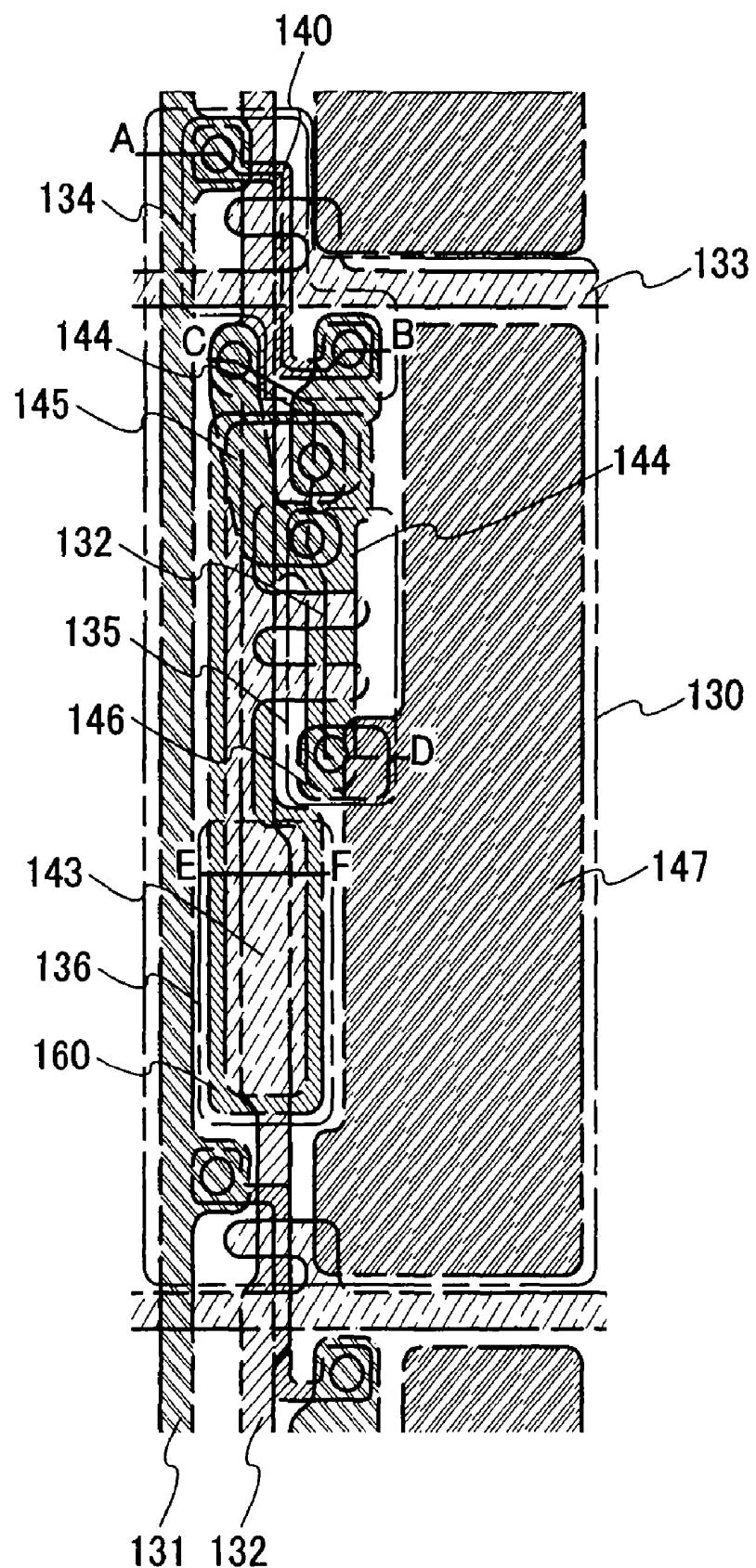

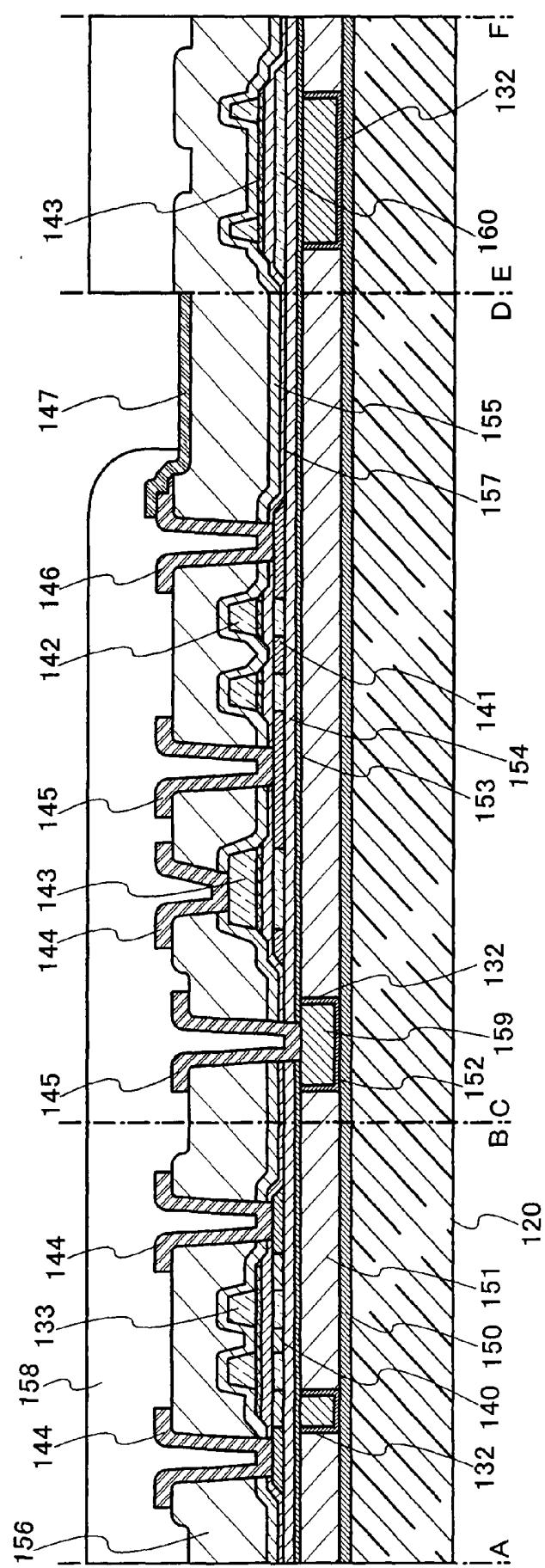

[0142] Next, an example of the subpixel 130 is described in details with reference to FIGS. 30 and 31. It is to be noted that FIG. 30 shows a top plan view of the subpixel 130 and FIG. 31 shows a longitudinal sectional view taken along lines A-B, C-D, and E-F in FIG. 30.

[0143] The scan line 133 and the data line 131 are formed of different layers and cross each other with an insulating layer 155 and an insulating layer 156 interposed therebetween. The scan line 133 functions as a gate electrode of a transistor at a portion where it crosses a semiconductor layer 141 with a gate insulating layer 157 interposed therebetween. In this case, by providing the transistor 134 in accordance with the arrangement of the semiconductor layer 141 and by branching the scan line 133 so that a plurality of parts intersect with the semiconductor layer 141, what is called a multi-gate transistor in which a plurality of channel forming regions are arranged in series between a pair of source and drain can be provided.

[0144] It is preferable that the resistance of the power supply line 132 connected to the transistor 135 be low, therefore, it is preferable to use Al, Cu, or the like having particularly low resistance for the power supply line 132. In the case of forming a Cu wire, the Cu wire can be formed in an insulating layer in combination with a barrier layer. FIG. 31 shows an example where the power supply line 132 is formed over the substrate 120 and under the semiconductor layer 141. A barrier layer 150 is formed over the surface of the substrate 120, thereby preventing impurities such as alkali metal contained in the substrate 120 from seeping. The power supply line 132 is formed of a barrier layer 152 and a Cu layer 159 in an opening formed in the insulating layer 151. The barrier layer 152 is formed of tantalum (Ta), tantalum nitride (TaN), tungsten nitride (WN), titanium nitride (TiN), or the like. The Cu layer 159 is formed by forming a seed layer by sputtering and accumulated in a thickness of 1 to 5 μm by plating, and planarized by chemical mechanical polishing. That is, by using damascene process, the Cu layer 159 can be embedded in the insulating layer 151.

[0145] A base insulating layer for semiconductor layers 140 and 141 is formed over the insulating layer 151. The structure of the base insulating layer is not limited, however, it is preferably formed of a silicon nitride layer 153 and a silicon oxide layer 154. Besides, as a structure of the insulating layer, an insulating layer 156 is formed of silicon

oxide, silicon nitride, or the like as a protective film over the semiconductor layers 140 and 141 in addition to the gate insulating layer 157.